Architecture dependent address space init.

Definition at line 40 of file as.c.

References as_ht_operations, as_operations, and asid_fifo_init().

Referenced by as_init().

Here is the call graph for this function:

|

|

Definition at line 47 of file as.h. Referenced by as_switch(). |

|

|

D-MMU ASIs. Definition at line 62 of file mmu.h. Referenced by dtlb_sfar_read(), dtlb_sfsr_read(), dtlb_sfsr_write(), dtlb_tag_access_read(), dtlb_tag_access_write(), mmu_primary_context_read(), mmu_primary_context_write(), mmu_secondary_context_read(), and mmu_secondary_context_write(). |

|

|

Definition at line 69 of file mmu.h. Referenced by dtlb_demap(). |

|

|

|

|

|

|

|

|

|

|

|

Definition at line 67 of file mmu.h. Referenced by dtlb_data_access_read(), and dtlb_data_access_write(). |

|

|

Definition at line 66 of file mmu.h. Referenced by dtlb_data_in_write(). |

|

|

Definition at line 68 of file mmu.h. Referenced by dtlb_tag_read_read(). |

|

|

I-MMU ASIs. Definition at line 47 of file mmu.h. Referenced by itlb_sfsr_read(), itlb_sfsr_write(), itlb_tag_access_read(), and itlb_tag_access_write(). |

|

|

Definition at line 53 of file mmu.h. Referenced by itlb_demap(). |

|

|

|

|

|

|

|

|

Definition at line 51 of file mmu.h. Referenced by itlb_data_access_read(), and itlb_data_access_write(). |

|

|

Definition at line 50 of file mmu.h. Referenced by itlb_data_in_write(). |

|

|

Definition at line 52 of file mmu.h. Referenced by itlb_tag_read_read(). |

|

|

LSU Control Register ASI. Load/Store Unit Control Register. Definition at line 44 of file mmu.h. Referenced by dmmu_set(), and immu_set(). |

|

|

|

|

|

Definition at line 109 of file mmu.h. Referenced by tlb_arch_init(). |

|

|

Definition at line 108 of file mmu.h. Referenced by tlb_arch_init(). |

|

|

|

|

|

Definition at line 39 of file frame.h. Referenced by anon_page_fault(), elf_frame_free(), elf_page_fault(), fast_data_access_mmu_miss(), ht_mapping_insert(), hw_map(), phys_page_fault(), and sys_physmem_map(). |

|

|

Definition at line 38 of file frame.h. Referenced by ADDR2PFN(), hw_map(), PFN2ADDR(), and SIZE2FRAMES(). |

|

|

Definition at line 107 of file mmu.h. Referenced by tlb_arch_init(). |

|

|

Definition at line 106 of file mmu.h. Referenced by tlb_arch_init(). |

|

|

Definition at line 46 of file tlb.h. Referenced by tlb_invalidate_all(), and tlb_print(). |

|

|

|

|

|

|

|

|

|

|

|

Bit width of the TLB-locked portion of kernel address space. Definition at line 56 of file tlb.h. Referenced by after_thread_ran_arch(), and before_thread_runs_arch(). |

|

|

|

Definition at line 40 of file page.h. Referenced by as_area_resize(), elf_frame_free(), elf_page_fault(), and hash(). |

|

|

Definition at line 53 of file tlb.h. Referenced by hw_map(), and tlb_arch_init(). |

|

|

Definition at line 52 of file tlb.h. Referenced by hw_map(). |

|

|

Definition at line 51 of file tlb.h. Referenced by hw_map(). |

|

|

Page sizes. Definition at line 50 of file tlb.h. Referenced by before_thread_runs_arch(), fast_data_access_mmu_miss(), and hw_map(). |

|

|

Definition at line 95 of file tlb.h. Referenced by tlb_arch_init(), and tlb_invalidate_asid(). |

|

|

Definition at line 100 of file tlb.h. Referenced by after_thread_ran_arch(), before_thread_runs_arch(), tlb_arch_init(), tlb_invalidate_asid(), and tlb_invalidate_pages(). |

|

|

TLB Demap Operation types. Definition at line 94 of file tlb.h. Referenced by after_thread_ran_arch(), before_thread_runs_arch(), and tlb_invalidate_pages(). |

|

|

TLB Demap Operation Context register encodings. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DMMU PA data watchpoint register. |

|

|

DMMU sync fault address register. Definition at line 76 of file mmu.h. Referenced by dtlb_sfar_read(). |

|

|

DMMU sync fault status register. Definition at line 75 of file mmu.h. Referenced by dtlb_sfsr_read(), and dtlb_sfsr_write(). |

|

|

DMMU TLB tag access register. Definition at line 78 of file mmu.h. Referenced by dtlb_tag_access_read(), and dtlb_tag_access_write(). |

|

|

Virtual Addresses within ASI_DMMU. DMMU tag target register. |

|

|

DMMU TSB base register. |

|

|

DMMU VA data watchpoint register. |

|

|

IMMU sync fault status register. Definition at line 57 of file mmu.h. Referenced by itlb_sfsr_read(), and itlb_sfsr_write(). |

|

|

IMMU TLB tag access register. Definition at line 59 of file mmu.h. Referenced by itlb_tag_access_read(), and itlb_tag_access_write(). |

|

|

Virtual Addresses within ASI_IMMU. IMMU tag target register. |

|

|

IMMU TSB base register. |

|

|

DMMU primary context register. Definition at line 73 of file mmu.h. Referenced by mmu_primary_context_read(), mmu_primary_context_write(), and mmu_secondary_context_write(). |

|

|

DMMU secondary context register. Definition at line 74 of file mmu.h. Referenced by mmu_secondary_context_read(). |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I-/D-TLB Data In/Access Register type. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Architecture dependent address space init. Definition at line 40 of file as.c. References as_ht_operations, as_operations, and asid_fifo_init(). Referenced by as_init(). Here is the call graph for this function:  |

|

|

Disable or Enable DMMU. Definition at line 123 of file mmu.h. References ASI_LSU_CONTROL_REG, asi_u64_read(), asi_u64_write(), lsu_cr_reg::dm, membar(), and lsu_cr_reg::value. Here is the call graph for this function:  |

|

|

Read DMMU TLB Data Access Register.

Definition at line 209 of file tlb.h. References ASI_DTLB_DATA_ACCESS_REG, asi_u64_read(), tlb_data_access_addr::tlb_entry, and tlb_data_access_addr::value. Here is the call graph for this function:  |

|

||||||||||||

|

Write DMMU TLB Data Access Register.

Definition at line 223 of file tlb.h. References ASI_DTLB_DATA_ACCESS_REG, asi_u64_write(), flush(), tlb_data_access_addr::tlb_entry, and tlb_data_access_addr::value. Here is the call graph for this function:  |

|

|

Write DMMU TLB Data in Register.

Definition at line 316 of file tlb.h. References ASI_DTLB_DATA_IN_REG, asi_u64_write(), and flush(). Referenced by dtlb_insert_mapping(), and tlb_arch_init(). Here is the call graph for this function:  |

|

||||||||||||||||

|

Perform DMMU TLB Demap Operation.

Definition at line 397 of file tlb.h. References ASI_DMMU_DEMAP, asi_u64_write(), tlb_demap_addr::context, flush(), tlb_demap_addr::type, tlb_demap_addr::value, and tlb_demap_addr::vpn. Referenced by after_thread_ran_arch(), before_thread_runs_arch(), tlb_arch_init(), tlb_invalidate_asid(), and tlb_invalidate_pages(). Here is the call graph for this function:  |

|

||||||||||||||||||||||||

|

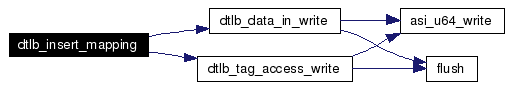

Insert privileged mapping into DMMU TLB.

Definition at line 134 of file tlb.c. References ASID_KERNEL, tte_data::cp, tte_data::cv, dtlb_data_in_write(), dtlb_tag_access_write(), tte_data::g, tte_data::l, tte_data::p, tte_data::pfn, tte_data::size, tte_data::v, tte_data::value, tlb_tag_read_reg::value, tlb_tag_read_reg::vpn, and tte_data::w. Referenced by before_thread_runs_arch(), fast_data_access_mmu_miss(), and hw_map(). Here is the call graph for this function:  |

|

|

Read DTLB Synchronous Fault Address Register.

Definition at line 364 of file tlb.h. References ASI_DMMU, asi_u64_read(), and VA_DMMU_SFAR. Here is the call graph for this function:  |

|

|

Read DTLB Synchronous Fault Status Register.

Definition at line 345 of file tlb.h. References ASI_DMMU, asi_u64_read(), and VA_DMMU_SFSR. Here is the call graph for this function:  |

|

|

Write DTLB Synchronous Fault Status Register.

Definition at line 354 of file tlb.h. References ASI_DMMU, asi_u64_write(), flush(), and VA_DMMU_SFSR. Here is the call graph for this function:  |

|

|

Read DMMU TLB Tag Access Register.

Definition at line 296 of file tlb.h. References ASI_DMMU, asi_u64_read(), and VA_DMMU_TAG_ACCESS. Referenced by fast_data_access_mmu_miss(). Here is the call graph for this function:  |

|

|

Write DMMU TLB Tag Access Register.

Definition at line 286 of file tlb.h. References ASI_DMMU, asi_u64_write(), flush(), and VA_DMMU_TAG_ACCESS. Referenced by dtlb_insert_mapping(), and tlb_arch_init(). Here is the call graph for this function:  |

|

|

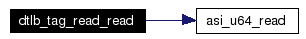

Read DMMU TLB Tag Read Register.

Definition at line 254 of file tlb.h. References ASI_DTLB_TAG_READ_REG, asi_u64_read(), tlb_data_access_addr::tlb_entry, and tlb_data_access_addr::value. Here is the call graph for this function:  |

|

|

DTLB miss handler. Definition at line 170 of file tlb.c. References ASID_KERNEL, tlb_tag_read_reg::context, dtlb_insert_mapping(), dtlb_tag_access_read(), FRAME_SIZE, get_symtab_entry(), PAGE_SIZE, PAGESIZE_8K, panic, printf(), tpc_read(), tlb_tag_read_reg::value, and tlb_tag_read_reg::vpn. Here is the call graph for this function:  |

|

|

DTLB protection fault handler. Definition at line 193 of file tlb.c. References panic. |

|

|

ITLB miss handler. Definition at line 164 of file tlb.c. References panic. |

|

|

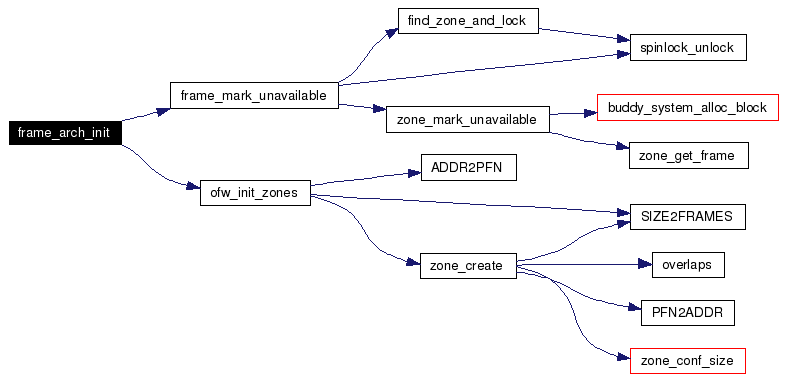

Definition at line 41 of file frame.c. References frame_mark_unavailable(), and ofw_init_zones(). Referenced by frame_init(). Here is the call graph for this function:  |

|

|

Definition at line 39 of file memory_init.c. References ofw_get_memory_size(). Referenced by main_bsp(). Here is the call graph for this function:  |

|

||||||||||||

|

Definition at line 47 of file page.c. References ASSERT, count, dtlb_insert_mapping(), fnzb32(), frame_alloc, FRAME_KA, FRAME_SIZE, FRAME_WIDTH, PAGE_SIZE, PAGESIZE_4M, PAGESIZE_512K, PAGESIZE_64K, PAGESIZE_8K, and PFN2ADDR(). Referenced by fb_init(), and kbd_init(). Here is the call graph for this function:  |

|

|

Disable or Enable IMMU. Definition at line 112 of file mmu.h. References ASI_LSU_CONTROL_REG, asi_u64_read(), asi_u64_write(), lsu_cr_reg::im, membar(), and lsu_cr_reg::value. Here is the call graph for this function:  |

|

|

Read IMMU TLB Data Access Register.

Definition at line 179 of file tlb.h. References ASI_ITLB_DATA_ACCESS_REG, asi_u64_read(), tlb_data_access_addr::tlb_entry, and tlb_data_access_addr::value. Referenced by tlb_invalidate_all(), and tlb_print(). Here is the call graph for this function:  |

|

||||||||||||

|

Write IMMU TLB Data Access Register.

Definition at line 193 of file tlb.h. References ASI_ITLB_DATA_ACCESS_REG, asi_u64_write(), flush(), tlb_data_access_addr::tlb_entry, and tlb_data_access_addr::value. Referenced by tlb_invalidate_all(). Here is the call graph for this function:  |

|

|

Write IMMU TLB Data in Register.

Definition at line 306 of file tlb.h. References ASI_ITLB_DATA_IN_REG, asi_u64_write(), and flush(). Referenced by tlb_arch_init(). Here is the call graph for this function:  |

|

||||||||||||||||

|

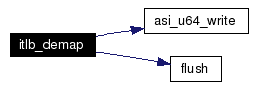

Perform IMMU TLB Demap Operation.

Definition at line 375 of file tlb.h. References ASI_IMMU_DEMAP, asi_u64_write(), tlb_demap_addr::context, flush(), tlb_demap_addr::type, tlb_demap_addr::value, and tlb_demap_addr::vpn. Referenced by tlb_arch_init(), tlb_invalidate_asid(), and tlb_invalidate_pages(). Here is the call graph for this function:  |

|

|

Read ITLB Synchronous Fault Status Register.

Definition at line 326 of file tlb.h. References ASI_IMMU, asi_u64_read(), and VA_IMMU_SFSR. Here is the call graph for this function:  |

|

|

Write ITLB Synchronous Fault Status Register.

Definition at line 335 of file tlb.h. References ASI_IMMU, asi_u64_write(), flush(), and VA_IMMU_SFSR. Here is the call graph for this function:  |

|

|

Read IMMU TLB Tag Access Register.

Definition at line 277 of file tlb.h. References ASI_IMMU, asi_u64_read(), and VA_IMMU_TAG_ACCESS. Here is the call graph for this function:  |

|

|

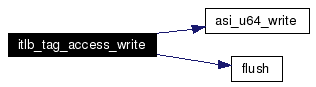

Write IMMU TLB Tag Access Register.

Definition at line 267 of file tlb.h. References ASI_IMMU, asi_u64_write(), flush(), and VA_IMMU_TAG_ACCESS. Referenced by tlb_arch_init(), and tlb_invalidate_all(). Here is the call graph for this function:  |

|

|

Read IMMU TLB Tag Read Register.

Definition at line 239 of file tlb.h. References ASI_ITLB_TAG_READ_REG, asi_u64_read(), tlb_data_access_addr::tlb_entry, and tlb_data_access_addr::value. Referenced by tlb_invalidate_all(), and tlb_print(). Here is the call graph for this function:  |

|

|

Read MMU Primary Context Register.

Definition at line 139 of file tlb.h. References ASI_DMMU, asi_u64_read(), and VA_PRIMARY_CONTEXT_REG. Here is the call graph for this function:  |

|

|

Write MMU Primary Context Register.

Definition at line 148 of file tlb.h. References ASI_DMMU, asi_u64_write(), flush(), and VA_PRIMARY_CONTEXT_REG. Here is the call graph for this function:  |

|

|

Read MMU Secondary Context Register.

Definition at line 158 of file tlb.h. References ASI_DMMU, asi_u64_read(), and VA_SECONDARY_CONTEXT_REG. Here is the call graph for this function:  |

|

|

Write MMU Primary Context Register.

Definition at line 167 of file tlb.h. References ASI_DMMU, asi_u64_write(), flush(), and VA_PRIMARY_CONTEXT_REG. Here is the call graph for this function:  |

|

|

Definition at line 42 of file page.c. References ht_mapping_operations. Referenced by page_init(). |

|

|

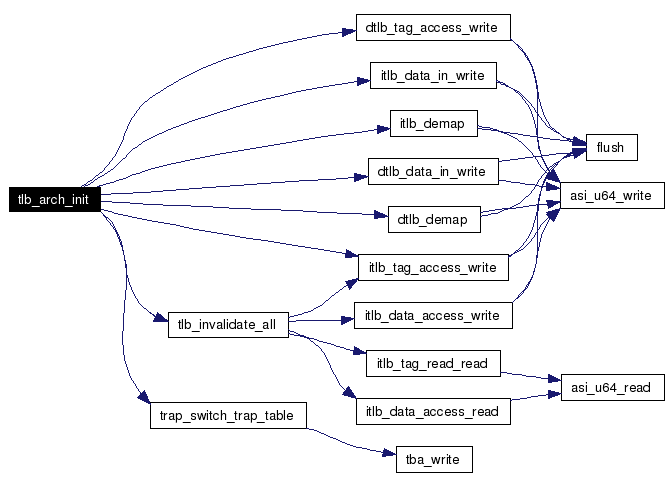

Initialize ITLB and DTLB. The goal of this function is to disable MMU so that both TLBs can be purged and new kernel 4M locked entry can be installed. After TLB is initialized, MMU is enabled again. Switching MMU off imposes the requirement for the kernel to run in identity mapped environment. Definition at line 71 of file tlb.c. References ASID_KERNEL, config_t::base, config, tte_data::cp, tte_data::cv, dmmu_disable, dmmu_enable, dtlb_data_in_write(), dtlb_demap(), dtlb_tag_access_write(), tte_data::g, immu_disable, immu_enable, itlb_data_in_write(), itlb_demap(), itlb_tag_access_write(), tte_data::l, tte_data::p, PAGESIZE_4M, tte_data::pfn, tte_data::size, TLB_DEMAP_CONTEXT, TLB_DEMAP_NUCLEUS, tlb_invalidate_all(), trap_switch_trap_table(), tte_data::v, tte_data::value, tlb_tag_read_reg::value, tlb_tag_read_reg::vpn, and tte_data::w. Referenced by tlb_init(). Here is the call graph for this function:  |

|

|

Invalidate all unlocked ITLB and DTLB entries. Definition at line 226 of file tlb.c. References itlb_data_access_read(), itlb_data_access_write(), ITLB_ENTRY_COUNT, itlb_tag_access_write(), itlb_tag_read_read(), tte_data::l, tte_data::v, tlb_tag_read_reg::value, and tte_data::value. Referenced by tlb_arch_init(), and tlb_shootdown_ipi_recv(). Here is the call graph for this function:  |

|

|

Invalidate all ITLB and DTLB entries that belong to specified ASID (Context).

Definition at line 258 of file tlb.c. References dtlb_demap(), itlb_demap(), TLB_DEMAP_CONTEXT, and TLB_DEMAP_NUCLEUS. Referenced by asid_get(), and tlb_shootdown_ipi_recv(). Here is the call graph for this function:  |

|

||||||||||||||||

|

Invalidate all ITLB and DTLB entries for specified page range in specified address space.

Definition at line 271 of file tlb.c. References dtlb_demap(), itlb_demap(), PAGE_SIZE, TLB_DEMAP_NUCLEUS, and TLB_DEMAP_PAGE. Referenced by tlb_shootdown_ipi_recv(). Here is the call graph for this function:  |

|

|

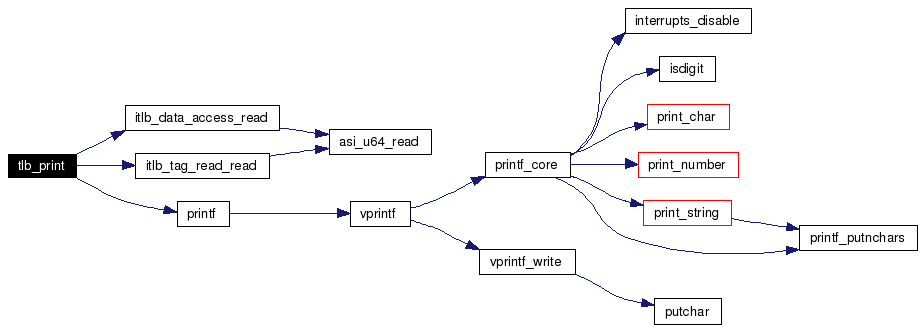

Print contents of both TLBs. Definition at line 199 of file tlb.c. References tlb_tag_read_reg::context, tte_data::cp, tte_data::cv, tte_data::diag, tte_data::e, tte_data::g, tte_data::ie, itlb_data_access_read(), ITLB_ENTRY_COUNT, itlb_tag_read_read(), tte_data::l, tte_data::nfo, tte_data::p, tte_data::pfn, printf(), tte_data::size, tte_data::soft, tte_data::soft2, tte_data::v, tlb_tag_read_reg::value, tte_data::value, tlb_tag_read_reg::vpn, and tte_data::w. Referenced by cmd_tlb(). Here is the call graph for this function:  |

|

|

Initial value: {

"Primary",

"Secondary",

"Nucleus",

"Reserved"

}

|

1.4.6

1.4.6