|

Files |

| file | as.h |

| file | asid.h |

| file | frame.h |

| file | memory_init.h |

| file | page.h |

| file | tlb.h |

| file | vhpt.h |

| file | as.c |

| file | frame.c |

| file | page.c |

| file | tlb.c |

| file | vhpt.c |

Data Structures |

| union | tlb_entry |

Defines |

| #define | KERNEL_ADDRESS_SPACE_SHADOWED_ARCH 0 |

| #define | KERNEL_ADDRESS_SPACE_START_ARCH (unsigned long) 0xe000000000000000ULL |

| #define | KERNEL_ADDRESS_SPACE_END_ARCH (unsigned long) 0xffffffffffffffffULL |

| #define | USER_ADDRESS_SPACE_START_ARCH (unsigned long) 0x0000000000000000ULL |

| #define | USER_ADDRESS_SPACE_END_ARCH (unsigned long) 0xdfffffffffffffffULL |

| #define | USTACK_ADDRESS_ARCH 0x0000000ff0000000ULL |

| #define | RIDS_PER_ASID 7 |

| #define | RID_MAX 262143 |

| #define | RID_KERNEL 0 |

| #define | RID_INVALID 1 |

| #define | ASID2RID(asid, vrn) (((asid)>RIDS_PER_ASID)?(((asid)*RIDS_PER_ASID)+(vrn)):(asid)) |

| #define | RID2ASID(rid) ((rid)/RIDS_PER_ASID) |

| #define | ASID_MAX_ARCH (RID_MAX/RIDS_PER_ASID) |

| #define | FRAME_WIDTH 14 |

| #define | FRAME_SIZE (1<<FRAME_WIDTH) |

| #define | get_memory_size() (512*1024*1024) |

| #define | PAGE_SIZE FRAME_SIZE |

| #define | PAGE_WIDTH FRAME_WIDTH |

| #define | tlb_arch_init() |

| #define | tlb_print() |

| #define | DTR_KERNEL 0 |

| #define | ITR_KERNEL 0 |

| #define | DTR_KSTACK1 1 |

| #define | DTR_KSTACK2 2 |

| #define | ROM_BASE 0xa0000 |

| #define | ROM_SIZE (384*1024) |

Typedefs |

| typedef __u16 | asid_t |

| typedef __u32 | rid_t |

| typedef tlb_entry | tlb_entry_t |

Functions |

| void | as_arch_init (void) |

| void | tc_mapping_insert (__address va, asid_t asid, tlb_entry_t entry, bool dtc) |

| void | dtc_mapping_insert (__address va, asid_t asid, tlb_entry_t entry) |

| void | itc_mapping_insert (__address va, asid_t asid, tlb_entry_t entry) |

| void | tr_mapping_insert (__address va, asid_t asid, tlb_entry_t entry, bool dtr, index_t tr) |

| void | dtr_mapping_insert (__address va, asid_t asid, tlb_entry_t entry, index_t tr) |

| void | itr_mapping_insert (__address va, asid_t asid, tlb_entry_t entry, index_t tr) |

| void | dtlb_kernel_mapping_insert (__address page, __address frame, bool dtr, index_t tr) |

| void | dtr_purge (__address page, count_t width) |

| void | dtc_pte_copy (pte_t *t) |

| void | itc_pte_copy (pte_t *t) |

| void | alternate_instruction_tlb_fault (__u64 vector, istate_t *istate) |

| void | alternate_data_tlb_fault (__u64 vector, istate_t *istate) |

| void | data_nested_tlb_fault (__u64 vector, istate_t *istate) |

| void | data_dirty_bit_fault (__u64 vector, istate_t *istate) |

| void | instruction_access_bit_fault (__u64 vector, istate_t *istate) |

| void | data_access_bit_fault (__u64 vector, istate_t *istate) |

| void | page_not_present (__u64 vector, istate_t *istate) |

| __address | vhpt_set_up (void) |

| static vhpt_entry_t | tlb_entry_t2vhpt_entry_t (tlb_entry_t tentry) |

| void | vhpt_mapping_insert (__address va, asid_t asid, tlb_entry_t entry) |

| void | vhpt_invalidate_all (void) |

| void | vhpt_invalidate_asid (asid_t asid) |

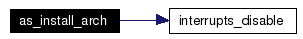

| void | as_install_arch (as_t *as) |

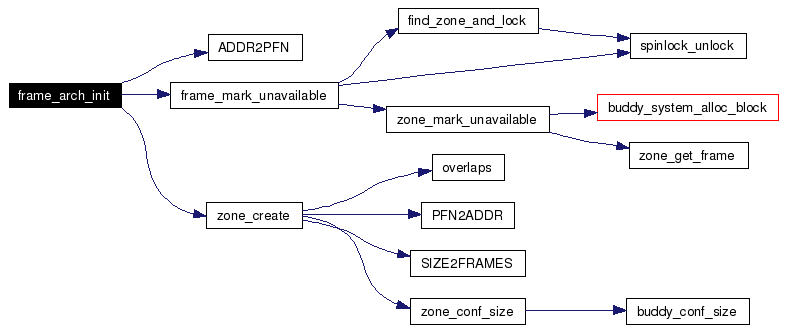

| void | frame_arch_init (void) |

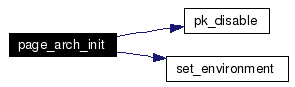

| static void | set_environment (void) |

| void | page_arch_init (void) |

| vhpt_entry_t * | vhpt_hash (__address page, asid_t asid) |

| bool | vhpt_compare (__address page, asid_t asid, vhpt_entry_t *v) |

| void | vhpt_set_record (vhpt_entry_t *v, __address page, asid_t asid, __address frame, int flags) |

| void | tlb_invalidate_all (void) |

| void | tlb_invalidate_asid (asid_t asid) |

| void | tlb_invalidate_pages (asid_t asid, __address page, count_t cnt) |

Variables |

| tlb_entry | packed |

| static vhpt_entry_t * | vhpt_base |

1.4.6

1.4.6