# Univerzita Karlova v Praze Matematicko-fyzikální fakulta

# DIPLOMOVÁ PRÁCE

Pavel Římský

## Podpora procesorů UltraSPARC III, IV, T1 a T2 v HelenOS

Katedra softwarového inženýrství

Vedoucí diplomové práce: Mgr. Martin Děcký

Studijní program: Informatika, Softwarové systémy

I would like to thank my supervisor Martin Děcký for reading the text of the thesis, for his suggestions, for negotiating the purchase of the Niagara-based machine by MFF UK and for administering the machine. I would like to thank Jakub Jermář for supervising the thesis from the very beginning, for lots of useful suggestions and for carefully reading the text of the thesis. I would like to thank the Prague globalization division of Sun Microsystems, namely Petr Štembera and Pavel Heimlich, for lending the SunBlade 1500 machine. I would like to thank Tomáš Hrubý for testing the Niagara port of HelenOS on his machine, which helped in overcoming a problem with starting application processors on Niagara.

Prohlašuji, že jsem svou diplomovou práci napsal samostatně a výhradně s použitím citovaných pramenů. Souhlasím se zapůjčováním práce.

V Praze dne

Pavel Římský

# Contents

| 1 | Intr | oductio                   | on                              | 10                 |

|---|------|---------------------------|---------------------------------|--------------------|

|   | 1.1  | Motiva                    | vation                          | <br>10             |

|   | 1.2  | Goals                     |                                 | <br>10             |

|   | 1.3  | Gettin                    | ng the Sources                  | <br>11             |

|   | 1.4  |                           | owledgements                    | 11                 |

|   | 1.5  |                           | to Read this Document           | 12                 |

|   |      |                           |                                 |                    |

| 2 |      |                           | Dverview                        | 13                 |

|   | 2.1  |                           | Management and Scheduling       | 13                 |

|   |      | 2.1.1                     | Threads                         | 13                 |

|   |      | 2.1.2                     | Fibrils                         | 14                 |

|   | 2.2  | ~                         | ronization                      | 14                 |

|   |      | 2.2.1                     | Active Primitives               | 14                 |

|   |      | 2.2.2                     | Passive Primitives              | 14                 |

|   | 2.3  |                           | ory Management                  | 14                 |

|   |      | 2.3.1                     | Frame Allocator                 | 14                 |

|   |      | 2.3.2                     | Slab Allocator                  | 14                 |

|   |      | 2.3.3                     | Virtual-to-physical Mapping     | <br>15             |

|   | 2.4  | Usersp                    | pace Support                    | <br>15             |

|   |      | 2.4.1                     | Passing Information from Kernel | 15                 |

|   |      | 2.4.2                     | IPC                             | <br>15             |

|   |      | 2.4.3                     | Important Servers               | <br>16             |

| 3 | 61 h | H CDA I                   | RC Processors Overview          | 17                 |

| 3 | 3.1  |                           | ters                            | 18                 |

|   | 5.1  | 3.1.1                     |                                 | 18                 |

|   |      | 3.1.1                     | General Purpose Registers       | 18                 |

|   |      | 3.1.2                     |                                 | 18                 |

|   |      | 3.1.3                     | Global Registers                | 10                 |

|   |      |                           | Windowed Registers              | 10<br>22           |

|   | 2 2  | 3.1.5                     | Control Registers               | 22                 |

|   | 3.2  | Traps                     |                                 |                    |

|   |      | 3.2.1                     | Trap Levels                     | 22                 |

|   |      | 3.2.2                     | Trap Table                      | 23                 |

|   | 0.0  | 3.2.3                     | Returning from a Trap           | 23                 |

|   | 3.3  |                           | $\operatorname{Dry}$            | 23                 |

|   |      | 3.3.1                     | Virtualization                  | 24                 |

|   |      | 3.3.2                     | Memory Access Instructions      | 24                 |

|   |      | 3.3.3                     | Address Space Identifiers       | 24                 |

|   |      | 3.3.4                     | Memory Contexts                 | 24                 |

|   |      | 3.3.5                     | Translation Lookaside Buffers   | 25                 |

|   |      | 3.3.6                     | Memory Management Traps         | 25                 |

|   |      | 3.3.7                     | Translation Storage Buffers     | 26                 |

|   | _    |                           |                                 |                    |

|   | 3.4  | 5.5.7<br>Interru<br>3.4.1 |                                 | <br>26<br>26<br>26 |

|   | 3.5         | 3.4.2<br>OpenH |                                      | 27<br>27    |

|---|-------------|----------------|--------------------------------------|-------------|

| 4 | IPS-        | compli         | ant Processors 2                     | 28          |

|   | <b>4</b> .1 |                |                                      | 28          |

|   |             | 4.1.1          |                                      | 9           |

|   | 4.2         |                |                                      | 9           |

|   |             | 4.2.1          |                                      | 9           |

|   |             | 4.2.2          |                                      | 9           |

|   |             | 4.2.3          | 0                                    | <br>81      |

|   |             | 4.2.4          | 0                                    | 32          |

|   | 4.3         | CPUs           |                                      | 32          |

|   | 1.0         | 4.3.1          |                                      | 32          |

|   |             | 4.3.2          |                                      | ,2<br>33    |

|   |             | 4.3.3          |                                      | 33          |

|   |             | 4.3.4          |                                      | ,5<br>33    |

|   |             | 4.3.4          | Inter-processor Interrupts           | 0           |

| 5 |             |                |                                      | <b>\$</b> 5 |

|   | 5.1         |                |                                      | 85          |

|   | 5.2         | <b>21</b>      |                                      | 86          |

|   |             | 5.2.1          |                                      | 86          |

|   |             | 5.2.2          |                                      | 87          |

|   |             | 5.2.3          | 1                                    | 88          |

|   | 5.3         |                |                                      | 39          |

|   |             | 5.3.1          |                                      | <u>8</u> 9  |

|   |             | 5.3.2          | 0                                    | 0           |

|   |             | 5.3.3          |                                      | 1           |

|   | 5.4         | Traps          |                                      | 1           |

|   |             | 5.4.1          | Privileged and Hyperprivileged Traps | 1           |

|   |             | 5.4.2          | Trap Levels                          | 1           |

|   | 5.5         | Miscel         |                                      | 2           |

|   |             | 5.5.1          | Scratchpad Registers                 | 2           |

|   |             | 5.5.2          | Some Hyperprivileged Registers       | 2           |

| 6 | Orig        | zinal U        | ltraSPARC HelenOS Port 4             | 4           |

|   | 6.1         | -              |                                      | 4           |

|   |             | 6.1.1          |                                      | 4           |

|   |             | 6.1.2          |                                      | 15          |

|   |             | 6.1.3          |                                      | 15          |

|   | 6.2         |                |                                      | 6           |

|   |             | 6.2.1          | 1 1                                  | 6           |

|   |             | 6.2.2          |                                      | 17          |

|   | 6.3         |                |                                      | 8           |

|   | 0.0         | 6.3.1          |                                      | 18          |

|   |             | 6.3.2          | 0                                    | 19          |

|   |             | 6.3.3          | 0 0                                  | 50          |

|   | 6.4         |                |                                      | 51          |

|   | 0.1         | 6.4.1          |                                      | 51          |

|   |             | 6.4.2          |                                      | 51          |

|   |             | 0.1.4          |                                      | · <b>T</b>  |

| 7 | Port                                                                        | ing He                                                                                                                                                                                   | lenOS to JPS Processors                                                                                                                                                 | 52                                                                                                                                             |

|---|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 7.1                                                                         | · ·                                                                                                                                                                                      |                                                                                                                                                                         | 52                                                                                                                                             |

|   |                                                                             | 7.1.1                                                                                                                                                                                    | Supported Environments                                                                                                                                                  | 52                                                                                                                                             |

|   |                                                                             | 7.1.2                                                                                                                                                                                    | Enhancements Overview                                                                                                                                                   | 52                                                                                                                                             |

|   |                                                                             | 7.1.3                                                                                                                                                                                    | Limitations                                                                                                                                                             | 52                                                                                                                                             |

|   |                                                                             | 7.1.4                                                                                                                                                                                    | Integration with the Original UltraSPARC Port                                                                                                                           | 53                                                                                                                                             |

|   | 7.2                                                                         | Sereng                                                                                                                                                                                   | geti and its Firmware                                                                                                                                                   | 54                                                                                                                                             |

|   |                                                                             | 7.2.1                                                                                                                                                                                    | SILO not Compatible with the Firmware                                                                                                                                   | 54                                                                                                                                             |

|   |                                                                             | 7.2.2                                                                                                                                                                                    | Other Serengeti Firmware Properties                                                                                                                                     | 55                                                                                                                                             |

|   | 7.3                                                                         | Memo                                                                                                                                                                                     | ry Subsystem                                                                                                                                                            | 56                                                                                                                                             |

|   |                                                                             | 7.3.1                                                                                                                                                                                    | Translation Lookaside Buffers                                                                                                                                           | 56                                                                                                                                             |

|   |                                                                             | 7.3.2                                                                                                                                                                                    | Caches                                                                                                                                                                  | 58                                                                                                                                             |

|   |                                                                             | 7.3.3                                                                                                                                                                                    | Miscellaneous                                                                                                                                                           | 59                                                                                                                                             |

|   | 7.4                                                                         | Proces                                                                                                                                                                                   | sors                                                                                                                                                                    | 60                                                                                                                                             |

|   |                                                                             | 7.4.1                                                                                                                                                                                    | Interconnect Bus Configuration Register                                                                                                                                 | 60                                                                                                                                             |

|   |                                                                             | 7.4.2                                                                                                                                                                                    |                                                                                                                                                                         | 60                                                                                                                                             |

|   |                                                                             | 7.4.3                                                                                                                                                                                    | Timer Interrupts                                                                                                                                                        | 60                                                                                                                                             |

|   |                                                                             | 7.4.4                                                                                                                                                                                    | CPU Models                                                                                                                                                              | 61                                                                                                                                             |

|   |                                                                             | 7.4.5                                                                                                                                                                                    |                                                                                                                                                                         | 62                                                                                                                                             |

|   | 7.5                                                                         | Device                                                                                                                                                                                   | e Drivers                                                                                                                                                               | 63                                                                                                                                             |

|   |                                                                             | 7.5.1                                                                                                                                                                                    |                                                                                                                                                                         | 63                                                                                                                                             |

|   |                                                                             | 7.5.2                                                                                                                                                                                    | Serengeti Console                                                                                                                                                       | 63                                                                                                                                             |

|   | 7.6                                                                         | Miscel                                                                                                                                                                                   | llaneous                                                                                                                                                                | 67                                                                                                                                             |

|   |                                                                             | 7.6.1                                                                                                                                                                                    | Setting Color Palette                                                                                                                                                   | 67                                                                                                                                             |

|   |                                                                             |                                                                                                                                                                                          |                                                                                                                                                                         |                                                                                                                                                |

| 8 | Port<br>8.1                                                                 | -                                                                                                                                                                                        | lenOS to sun4v Processors<br>iew                                                                                                                                        | <b>68</b><br>68                                                                                                                                |

| 8 |                                                                             | -                                                                                                                                                                                        | iew                                                                                                                                                                     |                                                                                                                                                |

| 8 |                                                                             | Overv                                                                                                                                                                                    | iew                                                                                                                                                                     | 68                                                                                                                                             |

| 8 |                                                                             | Overv<br>8.1.1<br>8.1.2<br>8.1.3                                                                                                                                                         | iew                                                                                                                                                                     | 68<br>68                                                                                                                                       |

| 8 |                                                                             | Overv<br>8.1.1<br>8.1.2<br>8.1.3                                                                                                                                                         | iew                                                                                                                                                                     | 68<br>68<br>68                                                                                                                                 |

| 8 | 8.1                                                                         | Overv<br>8.1.1<br>8.1.2<br>8.1.3                                                                                                                                                         | iew                                                                                                                                                                     | 68<br>68<br>68<br>68                                                                                                                           |

| 8 | 8.1                                                                         | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo                                                                                                                                               | iewSupported EnvironmentsSupported EnvironmentsEnhancements OverviewIntegration with the sun4u PortIntegration with the sun4u PortSupportader and Kernel StartupSupport | 68<br>68<br>68<br>68<br>70                                                                                                                     |

| 8 | 8.1                                                                         | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo<br>8.2.1<br>8.2.2                                                                                                                             | iewSupported EnvironmentsSupported EnvironmentsEnhancements OverviewIntegration with the sun4u Portwader and Kernel StartupBootloader                                   | 68<br>68<br>68<br>70<br>70                                                                                                                     |

| 8 | <ul><li>8.1</li><li>8.2</li></ul>                                           | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo<br>8.2.1<br>8.2.2                                                                                                                             | iewSupported EnvironmentsEnhancements OverviewIntegration with the sun4u Portader and Kernel StartupBootloaderKernel StartuprcallsPerforming Hypercalls from Assembly   | 68<br>68<br>68<br>70<br>70<br>72                                                                                                               |

| 8 | <ul><li>8.1</li><li>8.2</li></ul>                                           | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo<br>8.2.1<br>8.2.2<br>Hyper                                                                                                                    | iewSupported EnvironmentsEnhancements OverviewIntegration with the sun4u Portader and Kernel StartupBootloaderKernel StartuprcallsPerforming Hypercalls from Assembly   | 68<br>68<br>68<br>70<br>70<br>72<br>73                                                                                                         |

| 8 | <ul><li>8.1</li><li>8.2</li></ul>                                           | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlc<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1                                                                                                           | iew                                                                                                                                                                     | 68<br>68<br>68<br>70<br>70<br>72<br>73<br>74                                                                                                   |

| 8 | <ul><li>8.1</li><li>8.2</li></ul>                                           | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2                                                                                                  | iew                                                                                                                                                                     | 68<br>68<br>68<br>70<br>70<br>72<br>73<br>74<br>74                                                                                             |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li></ul>                               | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlc<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3                                                                                         | iew                                                                                                                                                                     | 68<br>68<br>68<br>70<br>70<br>72<br>73<br>74<br>74<br>75                                                                                       |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li></ul>                               | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs                                                                                 | iew                                                                                                                                                                     | 68<br>68<br>68<br>70<br>70<br>72<br>73<br>74<br>74<br>75<br>75                                                                                 |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li></ul>                               | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlc<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs<br>8.4.1<br>8.4.2                                                               | iew                                                                                                                                                                     | 68<br>68<br>68<br>70<br>70<br>72<br>73<br>74<br>74<br>75<br>75<br>75                                                                           |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li></ul>                   | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlc<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs<br>8.4.1<br>8.4.2                                                               | iew                                                                                                                                                                     | <ul> <li>68</li> <li>68</li> <li>68</li> <li>70</li> <li>70</li> <li>72</li> <li>73</li> <li>74</li> <li>75</li> <li>76</li> <li>76</li> </ul> |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li></ul>                   | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs<br>8.4.1<br>8.4.2<br>Memo                                                       | iew                                                                                                                                                                     | 68<br>68<br>70<br>70<br>72<br>73<br>74<br>74<br>75<br>75<br>76<br>76<br>76                                                                     |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li></ul>                   | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlc<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs<br>8.4.1<br>8.4.2<br>Memo<br>8.5.1                                              | iew                                                                                                                                                                     | $\begin{array}{c} 68\\ 68\\ 68\\ 70\\ 70\\ 72\\ 73\\ 74\\ 75\\ 75\\ 76\\ 76\\ 76\\ 76\\ 76\\ 76\end{array}$                                    |

| 8 | <ul><li>8.1</li><li>8.2</li><li>8.3</li><li>8.4</li></ul>                   | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs<br>8.4.1<br>8.4.2<br>Memo<br>8.5.1<br>8.5.2<br>8.5.3                            | iew                                                                                                                                                                     | $\begin{array}{c} 68\\ 68\\ 68\\ 70\\ 70\\ 72\\ 73\\ 74\\ 75\\ 75\\ 76\\ 76\\ 76\\ 76\\ 76\\ 77\\ \end{array}$                                 |

| 8 | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> </ul> | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlo<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs<br>8.4.1<br>8.4.2<br>Memo<br>8.5.1<br>8.5.2<br>8.5.3                            | iew                                                                                                                                                                     | $\begin{array}{c} 68\\ 68\\ 68\\ 70\\ 70\\ 72\\ 73\\ 74\\ 75\\ 75\\ 76\\ 76\\ 76\\ 76\\ 76\\ 77\\ 79\\ \end{array}$                            |

| 8 | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> </ul> | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlc<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs<br>8.4.1<br>8.4.2<br>Memo<br>8.5.1<br>8.5.2<br>8.5.3<br>Preem                   | iew                                                                                                                                                                     | $\begin{array}{c} 68\\ 68\\ 68\\ 70\\ 72\\ 73\\ 74\\ 75\\ 75\\ 76\\ 76\\ 76\\ 76\\ 76\\ 77\\ 79\\ 81 \end{array}$                              |

| 8 | <ul> <li>8.1</li> <li>8.2</li> <li>8.3</li> <li>8.4</li> <li>8.5</li> </ul> | Overv<br>8.1.1<br>8.1.2<br>8.1.3<br>Bootlc<br>8.2.1<br>8.2.2<br>Hyper<br>8.3.1<br>8.3.2<br>8.3.3<br>CPUs<br>8.4.1<br>8.4.2<br>Memo<br>8.5.1<br>8.5.2<br>8.5.3<br>Preem<br>8.6.1<br>8.6.2 | iew                                                                                                                                                                     | $\begin{array}{c} 68\\ 68\\ 68\\ 70\\ 72\\ 73\\ 74\\ 75\\ 75\\ 76\\ 76\\ 76\\ 76\\ 76\\ 79\\ 81\\ 82 \end{array}$                              |

|    |      | 8.7.2   | Input to Kernel                                      | 6 |

|----|------|---------|------------------------------------------------------|---|

|    |      | 8.7.3   | Userspace I/O Driver 86                              | 5 |

|    | 8.8  | Multip  | processing                                           | 7 |

|    |      | 8.8.1   | Waking the Application Processors up                 | 7 |

|    |      | 8.8.2   | Stopping the Application Processors                  | 3 |

|    |      | 8.8.3   | Setting the API Version                              | 3 |

|    |      | 8.8.4   | Problem Setting the API Version on Simics            | 3 |

|    |      | 8.8.5   | Problem Stopping CPUs on a Real Machine              | 3 |

|    |      | 8.8.6   | The Problem Solved                                   | 3 |

|    |      | 8.8.7   | Start of the Application Processors                  | 9 |

|    |      | 8.8.8   | Waking CPUs up: Comparison with the Original Port 90 | ) |

|    |      | 8.8.9   | Waking Processors up on Simics                       | ) |

|    |      | 8.8.10  | Inter-processor Interrupts                           | 1 |

|    |      | 8.8.11  | Optimal Scheduling                                   | 2 |

|    | 8.9  | UltraS  | PARC Architecture 2007                               | 1 |

| 9  | Rela | ted Wo  | rk 95                                                | 5 |

|    | 9.1  | Origin  | al HelenOS SPARC Port                                | 5 |

|    | 9.2  |         | HelenOS Ports                                        | 5 |

|    |      | 9.2.1   | Overview of HelenOS Ports                            | 5 |

|    |      | 9.2.2   | Inspiration by the Other Ports                       | 5 |

|    | 9.3  | Solaris | 96                                                   | 5 |

|    |      | 9.3.1   | Comparison with HelenOS                              | 5 |

|    | 9.4  | Linux   |                                                      | 7 |

|    |      | 9.4.1   | Comparison with HelenOS                              | 3 |

| 10 | Con  | clusion | 100                                                  | 0 |

|    | 10.1 | Enhan   | cements                                              | ) |

|    | 10.2 | Achiev  | rements                                              | 1 |

|    | 10.3 | Contri  | butions                                              | 1 |

|    | 10.4 | Perspe  | ctives                                               | 1 |

| 11 | Glos | sary    | 103                                                  | 3 |

| 12 | Bibl | iograpł | ny 105                                               | 5 |

# **List of Figures**

| 3 | 64-bit SPARC Processors Overview              |    |

|---|-----------------------------------------------|----|

|   | 3.1 Register Windows Arrangement              | 19 |

|   | 3.2 Overlapping of Registers.                 |    |

|   | 3.3 Example of Register Window Configuration. |    |

| 4 | JPS-compliant Processors                      |    |

|   | 4.1 Demap Address Format                      | 30 |

|   | 4.2 TSB Base Register format.                 | 31 |

| 5 | UltraSPARC Architecture 2005                  |    |

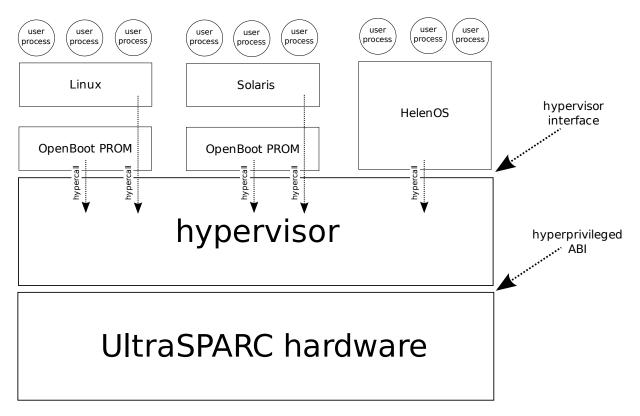

|   | 5.1 The sun4v Architecture                    |    |

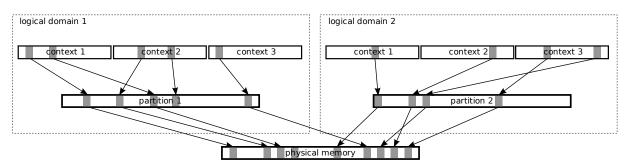

|   | 5.2 Two Levels of Memory Virtualization       | 39 |

| 6 | Original UltraSPARC HelenOS Port              |    |

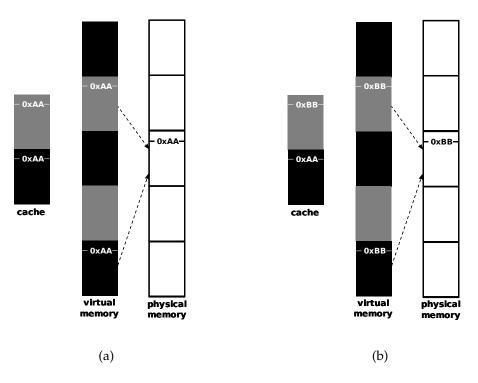

|   | 6.1 Illegal Alias                             | 50 |

|   |                                               |    |

# **List of Tables**

| 4  | JPS-compliant Processors4.1TLB sizes4.2Processor IDs                             |    |

|----|----------------------------------------------------------------------------------|----|

| 5  | UltraSPARC Architecture 2005<br>5.1 Trap Handling                                | 41 |

| 9  | Related Work9.1Comparison of the Current HelenOS Ports                           | 95 |

| 10 | Conclusion         10.1 Supported CPU models         10.2 Supported Environments |    |

*Název práce:* Podpora procesorů UltraSPARC III, IV, T1 a T2 v HelenOS *Autor:* Pavel Římský

Katedra (ústav): Katedra softwarového inženýrství

Vedoucí diplomové práce: Mgr. Martin Děcký

*e-mail vedoucího:* Martin.Decky@mff.cuni.cz

*Abstrakt:* Stručné představení operačního systému HelenOS. Přehled obecných vlastností 64-bitových procesorů SPARC (registry, trapy, jednotka správy paměti, OpenBoot PROM). Specifické vlastnosti procesorů vyhovujících JPS (Joint Programming Specification). Specifické vlastnosti procesorů Niagara a příbuzných procesorů (virtualizace, hypervisor, správa paměti). Představení původního portu systému HelenOS na procesory SPARC (bootování, preemptibilní handler trapů, správa paměti). Popis portu systému HelenOS na procesory vyhovující JPS (bootování, anomálie OBP, úpravy ve správci paměti, detekce konkrétního modelu procesoru, podpora pro dvoujádrové procesory, ovladač konzole na stroji Serengeti). Popis portu systému HelenOS na procesory Niagara (integrace s dalšími porty systému HelenOS na procesory SPARC, úpravy bootloaderu, převzetí TLB, volání hypervisoru, zpracování machine description, správa paměti, úpravy preemptibilního handleru trapů, ovladač vstupu a výstupu, podpora pro více procesorů, optimalizace plánovače). Přehled existujících portů systému HelenOS. Srovnání s původním portem systému HelenOS na procesory SPARC, srovnání s Linuxem a Solarisem.

Klíčová slova: operační systém, jádro, HelenOS, SPARC

*Title:* Support for UltraSPARC III, IV, T1 and T2 processors in HelenOS *Author:* Pavel Římský

Department: Department of Software Engineering

Supervisor: Mgr. Martin Děcký

*Supervisor's e-mail address:* Martin.Decky@mff.cuni.cz

*Abstract:* Overview of the HelenOS operating system. General overview of the 64bit SPARC processors (registers, traps, memory management unit, OpenBoot PROM). Overview of the specific features of the processors compliant with JPS (Joint Programming Specification). Overview of the specific features of the Niagara-based processors (virtualization, hypervisor, memory management). Overview of the original SPARC port of HelenOS (boot phase, preemptible trap handler, memory management). Description of the port of HelenOS onto the JPS-compliant processors (booting, OBP anomalies, modification of the memory management, detecting particular processor model, adding support for dual-core processors, driver of the Serengeti machine console). Description of the port of HelenOS onto the Niagara-based processors (integration with other SPARC HelenOS ports, bootloader modifications, taking over the TLB, hypercalls, parsing the machine description, memory management, preemptible trap handler modifications, input and output driver, multiprocessing, scheduler optimization). Overview of the existing HelenOS ports. Comparison with the original SPARC HelenOS port, comparison with Linux and Solaris.

Keywords: operating system, kernel, HelenOS, SPARC

# Chapter 1

## Introduction

### 1.1 Motivation

The world of today's computers is very diverse, spanning from small embedded devices to large servers. In the server machines, the maximum throughput and parallelism plays the most important role; such machines often contain tens of processors. In the past few years the producers have put an emphasis onto lowering the energy consumption, which lead to development of multicore processors where multiple central processing units are integrated in a single processor chip. Moreover, multithreaded processors have been introduced, which are able to execute multiple threads per one processor core in parallel, just by regularly switching among active register sets.

An interesting way how to investigate the features of the processors found in modern server machines is trying to add support for some selected family of those processors to some existing operating system which has not supported these processors so far.

This thesis describes the process of adding support for the newer 64-bit SPARC processors to the HelenOS operating system.

## 1.2 Goals

HelenOS is an experimental operating system being developed by volunteers – current and former students of Faculty of Mathematics and Physics of Charles University in Prague and a handful of external developers. It supports many processor architectures, among which there are the 64-bit SPARC processors. By the time the work on this thesis started, HelenOS had already supported some older 64-bit SPARC processor models. The aim of this thesis is to add support even for the newer 64-bit SPARC processor models so that all HelenOS features could be used on these models.

The processor models for which the support is intended are:

- the newer UltraSPARC III, IIIi, III+, IV and IV+ processors, and

- even newer UltraSPARC T1 and T2 processors.

The effort should result in a stable operating system with support for:

- multithreading,

- memory management,

- userspace,

- multiprocessor configurations.

This thesis introduces the newer SPARC processors, describes the process of porting HelenOS to those processors, and provides a comparison of the support for those processors in HelenOS with other operating systems.

## **1.3 Getting the Sources**

The sources are maintained in a Subversion repository. To get the trunk, use:

```

svn checkout \

svn://svn.helenos.org/HelenOS/trunk \

HelenOS

```

Apart from the trunk, a separate branch dedicated to this thesis called sparc exists. It is recommended to view the SVN log of the branch instead of the trunk to get a detailed overview of the changes made to the sources by the author of this thesis. Moreover, by the time this thesis was written, some changes from the branch had not been merged into the trunk yet. To check out the branch, use:

```

svn checkout \

svn://svn.helenos.org/HelenOS/branches/sparc \

HelenOS

```

## 1.4 Acknowledgements

The work on HelenOS (initially called *SPARTAN Kernel*) was started by Jakub Jermář. His work was joined by a group of other students of Faculty of Mathematics and Physics who extended HelenOS considerably and added support for a lot of new architectures. Support for the 64-bit SPARC processors was added by Jakub Jermář in 2006. Concurrently with the work on this thesis some new features were added to HelenOS. Let us point out

- loader, dynamic linker and debugger (by Jiří Svoboda),

- simple shell (by Tim Post),

- support for real-world Itanium servers (by Jakub Váňa) and

- a lot of further enhancements (by Jakub Jermář, Martin Děcký, Jiří Svoboda and others).

The code written as a part of this thesis is intermixed with the code written mainly as a part of [jj\_thesis]. It is contained mainly in the following directories:

- boot/arch/sparc64/loader,

- contrib/util,

- kernel/arch/sparc64,

- uspace/srv/fb and

- uspace/srv/kbd.

The code written as a part of this thesis is usually either located in a subdirectory called sun4v or it is inside a block delimited by #if defined (US3) and #endif directives. Some pieces of code which are a part of this thesis are, however, located in different places. Similarly some pieces of code which were *not* written as a part of this thesis have been borrowed and used in a sun4v directory or inside an #if .. #endif block. Thus, the only way how to reliably identify pieces of code written as a part of this thesis is inspecting the log of the spare branch of the HelenOS SVN repository.

## 1.5 How to Read this Document

In the text of this thesis the particular processor models are described and compared, the environments are briefly introduced, the original SPARC port is introduced and the enhancements done as a part of this thesis are explained.

Chapter 2 introduces the HelenOS operating system and its architecture.

Chapter 3 describes the very basic properties of the SPARC 64-bit processors which are common for all CPU models HelenOS supports.

Chapter 4 focuses on UltraSPARC III, III+, IIIi, IV and IV+ processors. In the chapter properties specific to these processors are introduced and where suitable, a comparison with their predecessors (UltraSPARC I, II and IIi) is provided.

In Chapter 5 the newest family of the SPARC 64-bit processors (UltraSPARC T1, T2) is introduced. Its basic features and properties are described.

Chapter 6 summarizes the implementation of the original port of HelenOS onto the SPARC 64-bit processors made by Jakub Jermář.

Then, the two most important chapters follow:

Chapter 7 describes the implementation of the port of HelenOS onto newer SPARC 64-bit processors (UltraSPARC III, III+, IIIi, IV and IV+).

Chapter 8 describes the implementation of the port of HelenOS onto the newest SPARC 64-bit processors (UltraSPARC T1, T2).

Chapter 9 compares the port to the newer and the newest SPARC processors with other HelenOS ports and with other operating systems.

Chapter 10 summarizes what has been achieved and outlines the perspectives of the work.

In Glossary 11 the reader can find definitions of the terms used throughout this book.

# **Chapter 2**

# **HelenOS** Overview

HelenOS is composed of a tiny microkernel and of servers – a set of userspace tasks providing basic operating system services. The microkernel is responsible for the time management, scheduling and synchronization, and memory management. The userspace servers implement the filesystems and drivers of devices such as frame-buffer, keyboard or RAM disk.

HelenOS design is thoroughly described in [helenos]<sup>1</sup>. In this chapter only the most significant design features are dealt with.

## 2.1 Time Management and Scheduling

Each processor regularly invokes a timer interrupt. HelenOS kernel handles these interrupts. Kernel uses these interrupts to

- keep track of the real time, and

- preempt the threads if they are running too long, so that no thread can usurp the whole CPU.

Upon a timer interrupt the kernel increments the variable representing the real time by a number of microseconds which have passed since the last timer interrupt.

#### 2.1.1 Threads

A thread is a basic unit of execution. An illusion is made that the threads run in parallel. On uniprocessor systems this is achieved by switching regularly among active threads (round robin with multilevel feedback, separate run queues for each CPU). On multiprocessor systems the threads may really run in parallel, each thread on its own CPU; if the number of threads exceeds the number of CPUs, threads are alternated on a particular CPU. To make all the CPUs roughly equally busy, a balancing thread is running on background. Each CPU has its own load balancing thread; when it detects that there are fewer ready threads than on an average CPU, it steels threads from the busy CPUs.

Each thread has its own stack. User processes are called *tasks* in HelenOS. A task is a group of threads which share the same virtual address space.

<sup>&</sup>lt;sup>1</sup>Unfortunately some portions of that document may be obsolete.

## 2.1.2 Fibrils

*Fibrils* are units of execution which are recognized purely by the userspace and which the kernel is not aware of. Several fibrils may be mapped onto one ordinary userspace thread.

## 2.2 Synchronization

### 2.2.1 Active Primitives

On the very low level, *spinlock* is used. The spinlock code tries to grab the lock by atomically setting the variable it is associated with using an architecture-dependent test-and-set instruction. If the variable is already set, the code actively waits (spins) until the variable becomes unset again, then it retries to grab the lock.

The spinlock code is usually optimized so that on uniprocessor systems only the preemption is disabled upon locking the spinlock, without spinning. On multiprocessors the preemption is disabled as well for the thread holding the lock, in order to prevent the priority inversion problem.

## 2.2.2 Passive Primitives

The basic passive synchronization primitive is called a *wait queue*. All other passive primitives build on it.

Wait queue allows a thread to sleep until an event associated with the queue occurs. If the event occurs before the thread starts to wait for it, it is recorded in a counter called *missed wakeups*. When some thread starts to wait for an event associated with a wait queue for which the missed wakeups variable is greater than zero, the missed wakeups variable is decremented by 1 and the thread does not have to sleep.

By pre-setting the missed wakeups to the number of threads which are allowed to enter a critical section, the wait queue will behave exactly as a semaphore (with the *wait* operation having the same effect as semaphore *down* operation and invoking the wait queue event having the same effect as the semaphore *up* operation).

Mutex is just a binary semaphore. Read-write lock is implemented in a way such that neither readers nor writers starve.

## 2.3 Memory Management

## 2.3.1 Frame Allocator

Upon startup, the kernel detects all available regions of the physical memory. The frame allocator allocates contiguous regions of physical memory, the size of the regions must be a power of two. For keeping track of all available regions of physical memory, buddy system is used.

## 2.3.2 Slab Allocator

Slab allocator allocates objects to be used by the kernel. A typical kernel object is small and kernel uses a lot of instances of the same type of object. Therefore it is reasonable to pre-allocate multiple objects of the same type at once, so that the average cost of an object allocation is low and memory fragmentation is minimized.

That is exactly what the slab allocator does. It pre-allocates multiple instances of objects of the same type. Pointers to those objects are stored in a cache and returned to the kernel when the kernel asks for the objects. Objects which the kernel does not use anymore are returned to the cache instead of being immediately deallocated.

If the kernel asks for an object type which the slab allocator has run out of, the slab allocator pre-allocates a new set of objects of that type. Similarly, if the kernel starts to run out of memory, the pre-allocated objects are deallocated.

The malloc function builds upon the slab allocator. The malloc function allocates pieces of memory whose sizes are multiples of two. Special 'pseudotypes' of objects are defined whose sizes are multiples of two. The malloc function then works by allocating instances of this 'pseudotype'.

### 2.3.3 Virtual-to-physical Mapping

HelenOS kernel makes use of paging. Segmentation is not used on any system which supports it, nor can the kernel run on MMU-less machines.

The virtual-to-physical mappings are stored in a structure called *page table*. On some architectures the page tables are managed by the hardware, while on others they are managed by the kernel. Anyway, the interface for accessing the page tables is unified in HelenOS. Three basic operations are defined: page\_mapping\_insert, p-age\_mapping\_find and page\_mapping\_remove. The actual implementation of these functions depends on the page table mechanism used for the given platform. HelenOS defines two page table mechanisms – global hashtable (where mappings of all the address spaces are stored) and hierarchical 4-level page tables.

## 2.4 Userspace Support

## 2.4.1 **Passing Information from Kernel**

Since kernel is able to gather some information about the host system which is not accessible by userspace, a mechanism for passing pieces of information from the kernel to userspace exists. The mechanism is called *sysinfo*. Kernel calls a special function, passing a string (as a key) and a number (as a value) to it. The userspace task then picks the value up by calling a function to which the key is passed. The sysinfo mechanism is commonly used by device drivers to pass the address where the device is mapped in the memory and other information.

## 2.4.2 IPC

*Interprocess communication* (IPC) is a mechanism via which the tasks communicate with each other. It is heavily used for communication between server tasks and ordinary applications. The IPC is asynchronous, analogous to phones (on the client side) and answerboxes (on the server side).

In order to make the IPC mechanism easily usable, a framework called *asynchronous framework* has been implemented. The asynchronous framework is described at the project wiki ([wiki]).

### 2.4.3 Important Servers

#### Name Server (ns)

The name server is a registry of all other servers. When a task needs to communicate with a certain server *S*, it asks the nameserver for a phone to *S*.

#### VFS Server (vfs) and Filesystem Servers

VFS server is a key server in the filesystem implementation. It accepts requests for filesystem operations from the tasks and dispatches them to servers which implement particular filesystems (TMPFS, FAT).

#### RAM Disk Server

The RAM disk server represents a virtual block device which uses physical memory as a storage. It is used by a filesystem implementation to store the initial user space environment (tasks, configuration, etc.).

#### Keyboard (kbd), Framebuffer (fb)

The keyboard server encapsulates drivers of several different keyboard models. The framebuffer server encapsulates

- drivers of several different framebuffer models, and

- drivers of several output devices which do not use a framebuffer (but for example a serial line).

The servers provide a unified interface to its clients, so that the clients do not have to bother with a particular type of input or output device.

#### Console

In the HelenOS user interface several virtual consoles may exist – each task that needs an output has its own virtual console. The user can switch between the consoles. The console server implements the virtual consoles mechanism.

# **Chapter 3**

# **64-bit SPARC Processors Overview**

This thesis deals with two architectures of the SPARC 64-bit processors. The first architecture conforms to the SPARC V9 specification [sparc\_v9] and it will be referred to as *sun4u* throughout the thesis. The second architecture follows the newer UltraSPARC Architecture 2005 specification [us2005hp] and will be referred to as *sun4v* throughout the thesis. Strictly speaking the terms *sun4u* and *sun4v* are commonly used to denote architecture of the whole machine rather than architecture of the processor. For sake of simplicity, however, in this thesis these terms will be used to denote architecture of the processors.

The SPARC V9 specification defines a common subset of properties that all conforming processor models must have. On the other hand, some properties<sup>1</sup> are left undefined in the SPARC V9 specification – they are further defined in so called *implementation supplements*. The SPARC V9-conformant processors can be logically grouped into

- the older models UltraSPARC I, UltraSPARC II, UltraSPARC IIe and UltraSPARC IIi, and

- the newer models UltraSPARC III, UltraSPARC IIIi, UltraSPARC III+, UltraSPARC IV and UltraSPARC IV+.

Processors from the same group are very similar to each other. Since processors from the former group have already been thoroughly described in [jj\_thesis], this thesis will only focus on processors from the latter group. Common properties of the processors from the latter group are summarized in a separate document called *Joint Programming Specification* [jps]<sup>2</sup>.

UltraSPARC Architecture 2005 specification defines common properties of the sun4v architecture processors. This thesis deals with the UltraSPARC T1 model (further described in UltraSPARC T1 Supplement [t1hp]) and the UltraSPARC T2 model.

This chapter summarizes common features of both the sun4u and the sun4v processors. Features which are specific to the particular architecture are summarized in Chapter 4 and Chapter 5.

<sup>&</sup>lt;sup>1</sup>Examples of such properties are: memory management unit, timer support, inter-processor interrupts and some special registers and instructions.

<sup>&</sup>lt;sup>2</sup>Joint Programming Specification is a common document created by Sun Microsystems and Fujitsu, as Fujitsu also manufactures JPS-compliant processors called *SPARC64<sup>®</sup> V*. Fujitsu models are, however, not covered in this thesis.

## 3.1 Registers

This section deals with general purpose registers and an assorted set of control registers.

## 3.1.1 General Purpose Registers

Code running on a 64-bit SPARC processor can access 32 non-privileged 64-bit integer registers at a given instant. These registers are denoted by symbols %r0 to %r31. They are partitioned into *global registers* (%r0 to %r7, commonly also denoted by symbols %g0 to %g7) and *windowed registers* (%r8 to %r31). Section 3.1.3 and Section 3.1.4 discuss both global and windowed registers thoroughly.

## 3.1.2 Control Registers

Control registers are privileged registers, which represent the current state of the CPU. They are discussed in Section 3.1.5.

## 3.1.3 Global Registers

Global register %g0 always reads as zero and writes to it are ignored.

There are multiple sets of global registers, but only one set is active at any given moment. A *normal globals* set is active when no trap is being processed. When a trap occurs, the normal globals set is shadowed by an alternative set. There are several alternative sets of global registers; the actual number and names of those alternative sets, however, depend on the architecture. See Section 4.1 for a description of the alternative sets of the global registers on the sun4u processors and Section 5.4 for a description of the alternative sets of the global registers on the sun4u processors.

## 3.1.4 Windowed Registers

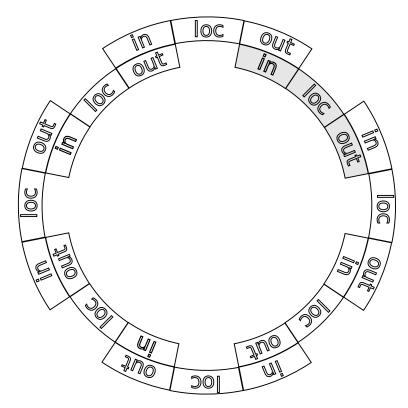

Registers %r8 to %r31 are called *windowed registers*. They are partitioned into

- output registers %r8 to %r15, also denoted by %00 to %07, which are used by a calling function to pass parameters to the callee and to read the return value,

- local registers %r16 to %r23, also denoted by %10 to %17, where the function can store values of its local variables, and

- input registers %r24 to %r31, also denoted by %i0 to %i7, which are used by a callee to read the parameters and pass the return value to the caller.

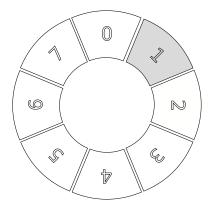

There are multiple sets of the windowed registers, but only one set is active at any given instant. A set of windowed registers is called a *register window*. The number of register windows is given by a CPU model-specific number NWINDOWS<sup>3</sup>. Register windows are numbered by numbers 0 to NWINDOWS - 1. The window which follows a window with number *n* has number (*n* + 1) modulo NWINDOWS. Therefore after the (NWINDOWS - 1)-th window a 0-th window logically follows, as depicted on Figure 3.1.

<sup>&</sup>lt;sup>3</sup>Which equals 8 on all processors mentioned in this thesis.

Register window with number 1 is the currently active window.

Figure 3.1: Register Windows Arrangement.

Functions store their local variables and call parameters to the active register window. During a function call a new register window is allocated, shadowing the register window of the caller. More precisely, in its prologue a function can issue the SAVE instruction, which results in deactivating the *n*-th register window and activating the (n + 1)-th (mod NWINDOWS) register window. Similarly, upon a return from a function call the current register window is deallocated and the register window of the caller becomes active again. More precisely, in its epilogue a function can issue the RESTORE instruction, which results in deactivating the (n + 1)-th window and re-activating the *n*-th window.

In order to make passing function parameters faster, output registers of the *n*-th register window overlap with the input registers of the (n + 1)-th register window. Hence performing the SAVE instruction causes that all values accessible via the output registers become accessible via the input registers. Overlapping of windows is depicted in Figure 3.2.

Figure 3.2: Overlapping of Registers.

If the SAVE instruction is issued and a new register window can not be allocated (there is a limited amount of register windows), a trap to the operating system is taken. Operating system copes with the situation by saving (in UltraSPARC terminology *spilling*) the oldest register window onto the stack. Similarly, if a RESTORE instruction is issued and the register window to which the code wishes to switch has been spilled to the stack, a trap to the operating system is taken. Operating system copes with the situation by reloading (in UltraSPARC terminology *filling*) the values from the stack to the register window.

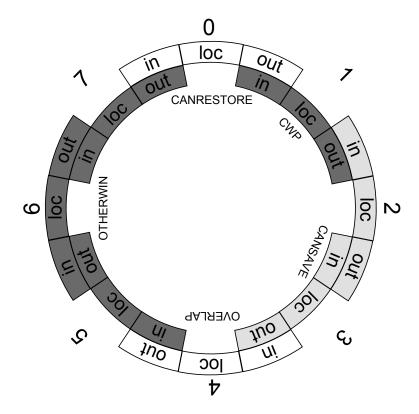

There is a handful of control registers which describe the configuration of register windows:

#### CWP, current window pointer

Contains the number of the currently active register window. It can contain values between 0 and NWINDOWS - 1.

#### CANSAVE

The value in the CANSAVE register denotes how many times the SAVE instruction can be issued before a spill trap will be generated.

#### CANRESTORE

The value in the CANRESTORE register denotes how many times the RESTORE instruction can be issued before a fill trap will be generated.

#### OTHERWIN

This register is used to mark a contiguous block of register windows which belong to a different address space and their spilling should be therefore performed by a different handler. Windows which belong to the different address space are called *other windows*. Windows which belong to the current address space are called *normal windows*.

The following equation holds:

CANSAVE + CANRESTORE + OTHERWIN + 1 + 1 = NWINDOWS.

The first "1" in the equation represents the current register window. The second "1" in the equation represents so called *overlap window*, which is a window whose output registers overlap with the input registers of the first occupied window and whose input registers, if all the windows had been occupied, would overlap with the output registers of the last window. An example register window configuration is depicted in figure Figure 3.3.

Window number 1 is the current window. Value of the CANSAVE register is 2, so the software can issue the SAVE instruction twice without invoking trap to the privileged software. Value of the CANRESTORE register is 1, which means that there is one more normal register window to which software can switch by issuing the RESTORE instruction without the need to reload register values from the memory stack. Value of the OTHERWIN register is 3, which means that there are three register windows which belong to a different address space and their spilling will be performed by a different spill handler. Window number 4 is an overlap window.

Figure 3.3: Example of Register Window Configuration.

Privileged software can define up to eight different spill handlers for normal windows and up to eight spill handlers for other windows. Similarly, privileged software can define up to eight different fill handlers for normal windows and up to eight fill handlers for other windows. The particular handler which will be used is selected according to the value of the WSTATE register<sup>4</sup>.

The last thing related to windowed registers worth mentioning is a special meaning of some registers. The %06 register, as defined by the application binary interface (ABI), is a *stack pointer*, i.e. an address of the top of the stack<sup>5</sup>. When the SAVE instruction is executed, the original value of the %06 register becomes accessible via the %16 register. The %16 register is also called a *frame pointer*, because its value represents an address<sup>6</sup> of the stack frame (the top of the stack of the calling function). The %07 register is a register where a calling function stores the values of its program counter when performing the call.

### 3.1.5 Control Registers

Here is a list of the very basic control registers, whose knowledge is recommended for understanding the ongoing parts of this thesis.

#### PC, program counter

Contains the address of the instruction being currently executed.

#### NPC, next program counter

Contains the address of the instruction which is to be executed next.

#### PSTATE, processor state

Encapsulates values of several flags, such as the privilege level or the active set of global registers.

## 3.2 Traps

A *trap* is a transfer of control to the privileged software. Examples of traps on 64-bit SPARC processors include

- register window spills and fills (see Section 3.1.4),

- memory management exceptions,

- illegal instructions,

- hardware, inter-processor and timer interrupts.

### 3.2.1 Trap Levels

SPARC 64-bit processors allow nested traps. When a trap is being processed, another trap can come and be processed without destroying the state of the first trap. The depth of trap nesting is limited, though. The depth depends on the processor architecture, but it is usually not bigger than five levels. The current trap level is represented by the

<sup>&</sup>lt;sup>4</sup>The WSTATE register has six significant bits. Bits 0 to 2 contain the index of the spill (fill) handler which will be used should the normal window trap. Bits 3 to 5 contain the index of the spill (fill) handler which will be used should the other window trap.

<sup>&</sup>lt;sup>5</sup>Address of the top of the stack is actually equal to 006 + 0x7ff.

<sup>&</sup>lt;sup>6</sup>Address of the top of the stack frame is actually equal to \$i6 + 0x7ff.

value of the TL register. When no trap is being processed, the TL register has value 0. When a trap comes, the value of the TL register is increased by one.

When a trap comes, the state of the processor is snapshotted to special registers so that it can be renewed as soon as the trap is processed. The registers are as follows:

#### TSTATE

Encapsulates the value of the CWP and PSTATE registers and other essential state valid at the time the trap was taken.

#### TPC

Contains the value of the PC register valid at the time the trap was taken.

TNPC

Contains the value of the NPC register valid at the time the trap was taken.

There are multiple sets of TSTATE, TPC and TNPC registers, the number of the sets equals to the number of trap levels above zero. If TL equals n > 0, the TSTATE, TPC and TNPC registers always contain the state of the CPU valid the last time when TL was equal to n - 1.

## 3.2.2 Trap Table

The type of the trap can be determined from the TT (*trap type*) register. The TT register contains a number between 0 and 511, which acts as an index to the trap table. Each entry in the trap table is a sequence of a limited number of instructions (32 for the most common types, 8 for other types). The table is partitioned into two parts, the first part contains trap handlers which will be invoked if the trap occurs when TL = 0, the second part contains handlers which will be invoked if the trap occurs when TL > 0.

Trap table is placed in the main memory, its address is set using the privileged TBA (trap base address) register.

## 3.2.3 Returning from a Trap

There are two instructions for returning from a trap: DONE and RETRY. They both decrease the trap level (TL) by one and restore the state saved in TSTATE, TPC and TNPC registers. After the DONE instruction the control is transferred to the instruction which follows the instruction last executed before the trap. After the RETRY instruction the control is transferred to the instruction the instruction last executed before the trap. After the registers that the instruction last executed before the trap is re-executed.

## 3.3 Memory

This section describes how memory is virtualized on UltraSPARC processors, introduces memory access instructions and mentions how to access special registers using these instructions.

## 3.3.1 Virtualization

UltraSPARC processors are equipped with a memory management unit which translates virtual page numbers onto physical frame numbers<sup>7</sup>. The translations are managed entirely by software, hardware provides only a small but fast cache of translations called *translation lookaside buffer*. The MMU supports 8 kB, 64 kB, 512 kB, and 4 MB page sizes.

Address translation mechanism can be split so that one translation mechanism is used for instructions and a different one for data, even though the same physical memory is still used. Privileged software may, however, keep the same virtual-to-physical mappings for both instructions and data.

## 3.3.2 Memory Access Instructions

There are only a few instructions for memory access: load instructions, store instructions and load-store instructions (which are used for synchronization purposes). All arithmetical and logical operations are performed purely on registers without interacting with memory. Load and store instructions are used not only to access memory, but also to access I/O address spaces and some special registers.

## 3.3.3 Address Space Identifiers

When issuing a load or store instruction, an *address space identifier* (ASI) can be specified as one of the instruction arguments. Address space identifier is a number between 0 and 255. Generally speaking, the address space identifier determines how the load or store instruction is to be interpreted. Address space identifier influences

- whether an ordinary memory or a special register is accessed,

- whether accessing the address has a side effect (accessing I/O addresses),

- whether the data being loaded/stored are big-endian or little-endian,

- whether the memory management unit is bypassed (no virtual address translation),

- which virtual address space (*context* is SPARC terminology) is accessed,

- and other issues.

## 3.3.4 Memory Contexts

Virtual address spaces are called *contexts*. Memory management unit may concurrently keep track of up to 2<sup>13</sup> contexts. Contexts are distinguished by *context identifiers*<sup>8</sup>, numbers between 0 and 2<sup>13</sup> - 1.

<sup>&</sup>lt;sup>7</sup>On UltraSPARC Architecture 2005 it is a little bit more complicated.

<sup>&</sup>lt;sup>8</sup>The term 'context' is also known as ASID on some architectures, do not confuse with ASI.

#### **Context Registers**

Three contexts may be active concurrently. Which one of the three contexts will be used for particular memory operations depends on the ASI used and on the current trap level.

#### NUCLEUS

This context is used when the trap level (TL) is greater than 0, i.e. when a trap is being processed. The context ID is hardwired to 0.

#### PRIMARY

Context used for normal memory access. Normal memory access is access with ASI equal to ASI\_PRIMARY<sup>9</sup>. This context's ID is stored in the *Primary Context Register*.

#### SECONDARY

Context used for memory access using ASI equal to ASI\_SECONDARY. Whether and how the access via ASI\_SECONDARY is used depends purely on the software. This context's ID is stored in the *Secondary Context Register*.

### 3.3.5 Translation Lookaside Buffers

Translation tables are software-managed on the 64-bit SPARC processors. Hardware keeps track of a limited set of translations in a *translation lookaside buffer* (TLB). There are separate TLBs for instruction and data memory. The instruction TLB is commonly referred to as ITLB and the data TLB is commonly referred to as DTLB. Depending on the architecture, the TLB contains between 64 and 512 entries. On some architectures there may be more than one ITLB and more than one DTLB in one memory management unit.

#### **Translation Table Entry**