# HelenOS 0.2.0

design documentation

June 18, 2006

HelenOS 0.2.0

# Contents

| 1 | Introduction         1.1 How to Read This Book                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Architecture Overview       2.1       Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3 | Data Structuresa3.1Lists3.2FIFO Queues3.3Hash Tables3.4Bitmaps3.5B+trees10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4 | Time Management114.1System Clock14.2Timeouts124.3Generic Clock Interrupt Handler124.4Time Source for Userspace12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5 | Scheduling       14         5.1       Contexts       14         5.1.1       Synchronous Context Switches       14         5.2       Threads       14         5.3       Scheduler       14         5.3.1       Run Queues       14         5.3.2       Scheduler Operation       14         5.3.3       Processor Load Balancing       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6 | Synchronization186.1Introduction186.2Active Kernel Primitives186.2.1Spinlocks186.3Passive Kernel Synchronization196.3.1Wait Queues196.3.2Semaphores196.3.3Mutexes206.3.4Reader/Writer Locks206.3.5Condition Variables216.4Userspace Synchronization226.4Futexes22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7 | Memory management       24         7.1       Physical memory management       24         7.1.1       Zones and frames       24         7.1.2       Frame allocator       24         7.1.3       Buddy allocator       24         7.1.4       Slab allocator       24         7.1.4       Slab allocator       24         7.1.4       Number of the second sec |

|   |                   |                                                                                                                                  | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29<br>29                                                                         |  |

|---|-------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

|   | 7.3               | Tranch                                                                                                                           | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29<br>29                                                                         |  |

|   | 7.5               | 7.3.1                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29<br>31                                                                         |  |

|   | 7.4               |                                                                                                                                  | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                                                               |  |

|   | 7.4               |                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31                                                                               |  |

|   |                   | 7.4.1                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31<br>32                                                                         |  |

|   |                   |                                                                                                                                  | 5 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |  |

|   |                   | 740                                                                                                                              | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32                                                                               |  |

|   |                   | 7.4.2                                                                                                                            | Address Space ID (ASID)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 32                                                                               |  |

| 8 | IPC               |                                                                                                                                  | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34                                                                               |  |

| 0 | 8.1               | Kornol                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                                                               |  |

|   | 0.1               | 8.1.1                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34                                                                               |  |

|   |                   | 8.1.2                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35                                                                               |  |

|   | 8.2               |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36                                                                               |  |

|   | 0.2               | -                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36                                                                               |  |

|   |                   | 8.2.1                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |  |

|   |                   | 8.2.2                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36                                                                               |  |

|   |                   | 8.2.3                                                                                                                            | The Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                                                               |  |

| 9 | 9 Device Drivers  |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |  |

| , | 9.1               |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>39</b><br>39                                                                  |  |

|   | 9.2               |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39                                                                               |  |

|   | 9.2<br>9.3        |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39<br>39                                                                         |  |

|   | 9.5               | DISabi                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 59                                                                               |  |

| Α | Arcl              | Architecture Specific Notes 4                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |  |

|   |                   |                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |  |

|   |                   |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                               |  |

|   |                   | A.1.1                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40<br>40                                                                         |  |

|   |                   |                                                                                                                                  | Virtual Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40                                                                               |  |

|   |                   | A.1.2                                                                                                                            | Virtual Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40<br>40                                                                         |  |

|   |                   | A.1.2<br>A.1.3                                                                                                                   | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40<br>40<br>40                                                                   |  |

|   |                   | A.1.2<br>A.1.3<br>A.1.4                                                                                                          | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40<br>40<br>40<br>40                                                             |  |

|   |                   | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5                                                                                                 | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40<br>40<br>40<br>40<br>41                                                       |  |

|   | Δ 2               | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6                                                                                        | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 40<br>40<br>40<br>41<br>41                                                       |  |

|   |                   | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA                                                                            | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4         A-32       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40<br>40<br>40<br>41<br>41<br>41                                                 |  |

|   |                   | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I                                                                | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4         A-32       4         MIPS       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40<br>40<br>40<br>41<br>41<br>41<br>41                                           |  |

|   |                   | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1                                                       | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4         A-32       4         MIPS       4         Thread Local Storage       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41                                     |  |

|   | A.3               | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1<br>A.3.2                                              | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4         A-32       4         MIPS       4         Thread Local Storage       4         Lazy FPU Context Switching       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41<br>41<br>41                         |  |

|   | A.3               | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1<br>A.3.2<br>Power                                     | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4         A-32       4         MiIPS       4         Thread Local Storage       4         PC       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41<br>42<br>42                         |  |

|   | A.3               | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1<br>A.3.2<br>Power<br>A.4.1                            | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4         A-32       4         MIPS       4         Thread Local Storage       4         Azy FPU Context Switching       4         PC       4         OpenFirmware Boot       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41<br>42<br>42<br>42                   |  |

|   | A.3<br>A.4        | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1<br>A.3.2<br>Power<br>A.4.1<br>A.4.2                   | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4         A-32       4         MIPS       4         Thread Local Storage       4         QpenFirmware Boot       4         Thread Local Storage       4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41<br>42<br>42<br>42<br>42             |  |

|   | A.3<br>A.4        | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1<br>A.3.2<br>Power<br>A.4.1<br>A.4.2<br>IA-64          | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       4         Thread Local Storage       4         Fast SYSCALL/SYSRET Support       4         Debugging Support       4         A-32       4         MIPS       4         Thread Local Storage       4         Collector       4         OpenFirmware Boot       4         Thread Local Storage       4         OpenFirmware Boot       4         Thread Local Storage       4         OpenFirmware Boot       4         Thread Local Storage       4                                                                                                                                                                                                                                                                                                   | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41<br>42<br>42<br>42<br>42<br>42       |  |

|   | A.3<br>A.4        | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1<br>A.3.2<br>Power<br>A.4.1<br>A.4.2<br>IA-64<br>A.5.1 | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       6         Thread Local Storage       6         Fast SYSCALL/SYSRET Support       6         Debugging Support       6         A-32       6         MIPS       6         Lazy FPU Context Switching       6         PC       6         OpenFirmware Boot       6         Thread Local Storage       6         Thread Local Storage       6         OvenFirmware Boot       6         Thread Local Storage       6         Thread Local Storage       6         Miread Local Storage       6         Thread Local Storage       6 <th>40<br/>40<br/>40<br/>41<br/>41<br/>41<br/>41<br/>41<br/>42<br/>42<br/>42<br/>42<br/>42<br/>42</th> | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41<br>42<br>42<br>42<br>42<br>42<br>42 |  |

|   | A.3<br>A.4        | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1<br>A.3.2<br>Power<br>A.4.1<br>A.4.2<br>IA-64          | Virtual Memory       4         TLB-only Paging       4         Mapping of Physical Memory       6         Thread Local Storage       6         Fast SYSCALL/SYSRET Support       6         Debugging Support       6         A-32       6         MIPS       6         Thread Local Storage       6         Lazy FPU Context Switching       6         PC       7         OpenFirmware Boot       6         Thread Local Storage       6         Thread Local Storage       6         OpenFirmware Boot       6         Thread Local Storage       6         Miread Local Storage       6         Thread Local Storage       6         Thread Local Storage       6         Miread Local Storage       6         Thread Local Storage       6         Miread Local Storage       6 <th>40<br/>40<br/>40<br/>41<br/>41<br/>41<br/>41<br/>41<br/>41<br/>42<br/>42<br/>42<br/>42<br/>42</th> | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41<br>41<br>42<br>42<br>42<br>42<br>42 |  |

| В | A.3<br>A.4<br>A.5 | A.1.2<br>A.1.3<br>A.1.4<br>A.1.5<br>A.1.6<br>Intel IA<br>32-bit I<br>A.3.1<br>A.3.2<br>Power<br>A.4.1<br>A.4.2<br>IA-64<br>A.5.1 | Virtual Memory4TLB-only Paging6Mapping of Physical Memory7Thread Local Storage7Fast SYSCALL/SYSRET Support7Debugging Support7A-327VIIPS7Thread Local Storage7Lazy FPU Context Switching7PC7OpenFirmware Boot7Thread Local Storage7Thread Local                                                                                                                                                                                                                                                         | 40<br>40<br>40<br>41<br>41<br>41<br>41<br>41<br>42<br>42<br>42<br>42<br>42<br>42 |  |

Index

45

# **List of Figures**

| 2 | Architecture Overview         2.1       HelenOS architecture overview.       6                                                                                                       |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

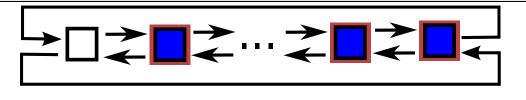

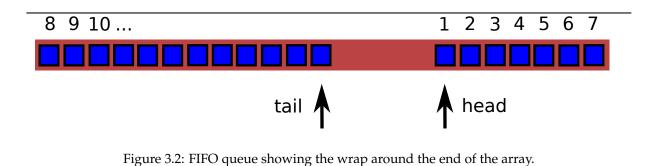

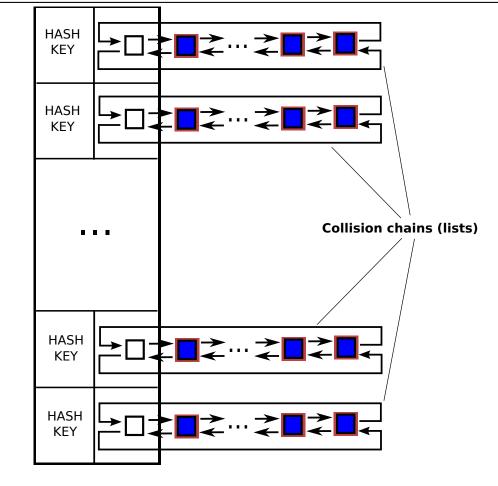

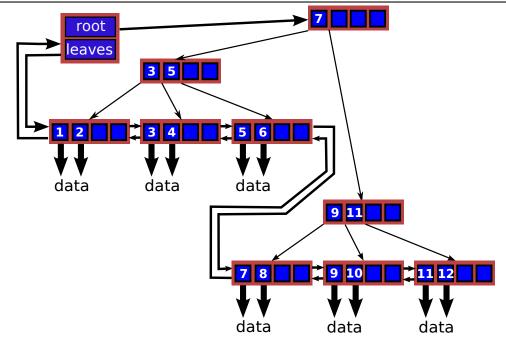

| 3 | Data Structures3.1Doubly-circularly-linked list83.2FIFO queue showing the wrap around the end of the array.93.3Generic hash table.93.4B+tree containing keys ranging from 1 to 12.10 |

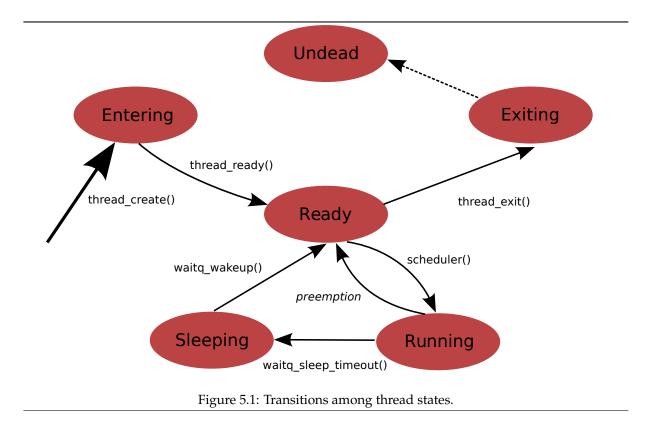

| 5 | Scheduling         5.1       Transitions among thread states.       16                                                                                                               |

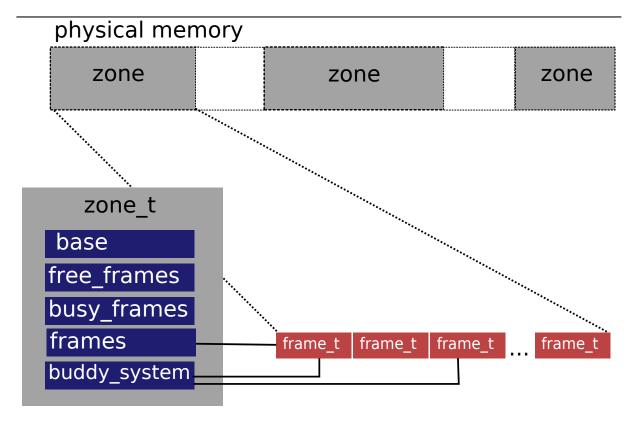

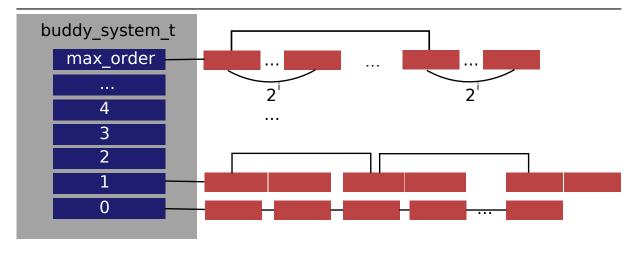

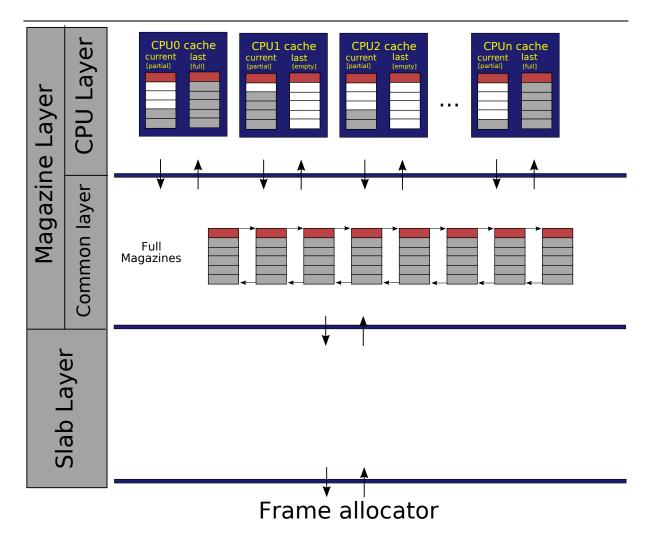

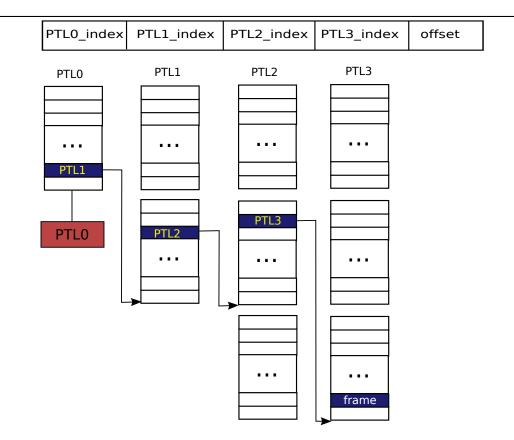

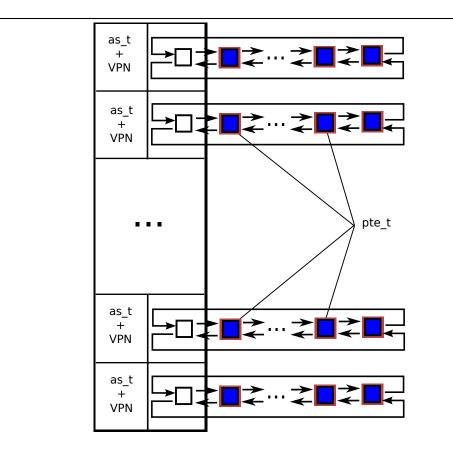

| 7 | Memory management257.1Frame allocator scheme.257.2Buddy system scheme.267.3Slab allocator scheme.277.4Hierarchical 4-level page tables.307.5Global page hash table.30                |

| 8 | IPC         8.1       Low level IPC       35         8.2       Single point of entry       37         8.3       Single point of entry solution       37                              |

| A | Architecture Specific Notes       41         A.1 IA-32 & AMD64 TLD       41         A.2 MIPS & PowerPC TLD       42         A.3 IA-64 TLD       43                                   |

# Introduction

HelenOS is a portable operating system with support for a variety of modern processor architectures<sup>1</sup>.

This book describes the design and principles of the HelenOS operating system from the perspective of its microkernel as well as from the perspective of its userspace drivers and server tasks. Its primary goal is to present ideas behind each subsystem and highlight things that are specific to HelenOS. Although this text contains references to source code (e.g. function names), these are provided only to improve reader's orientation when reading the code. This book does not attempt to be a substitute for a reference manual and the reader is strongly encouraged to look for interface details there.

#### 1.1 How to Read This Book

Chapter 2 contains overview of the overall HelenOS architecture.

Chapter 3 describes essential data structures used both in the kernel and in the userspace.

Chapter 4 focuses on time management in the kernel and scheds some light on the userspace source of time.

Chapter 5 is dedicated to threads and the scheduling subsystem.

Chapter 7 describes memory management of physical and virtual memory.

Chapter 8 deals with the IPC subsystem.

Chapter 9 describes facilities that a userspace task can use in order to become a device driver. Appendix A presents some architecture specific issues.

<sup>&</sup>lt;sup>1</sup> amd64, ia32, ia64, mips32 and ppc32.

# **Architecture Overview**

The HelenOS operating system is designed as a relatively small microkernel assisted with a set of userspace drivers and server tasks. HelenOS is not very radical in which subsystems should or should not be implemented in the kernel - in some cases, both kernel and userspace drivers exist. The reason for creating the system as a microkernel is prosaic. Even though it is initially more difficult to get the same level of functionality from a microkernel than it is in the case of a simple monolithic kernel, a microkernel is much easier to maintain once the pieces have been put to work together. Therefore, the kernel of HelenOS, as well as the essential userspace libraries thereof can be maintained by only a few developers who understand them completely. In addition, a microkernel based operating system reaches completion sooner than monolithic kernels as the system can be used even without some traditional subsystems (e.g. block devices, filesystems and networking).

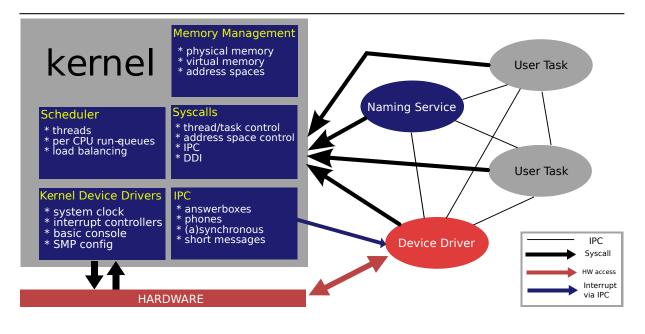

Figure 2.1: HelenOS architecture overview.

HelenOS is comprised of the kernel and the userspace server tasks. The kernel provides scheduling, memory management and IPC. It also contains essential device drivers that control the system clock and other devices necessary to guarantee a safe environment. Userspace communicates with the kernel through a small set of syscalls. The userspace layer consists of tasks with different roles, capabilities and privileges. Some of the tasks serve as device drivers, naming servers, managers of various kinds and some are just ordinary user programs. All of them communicate with other threads via kernel-provided IPC.

# 2.1 Scheduling

Kernel's unit of execution flow is a thread. A thread is an entity that executes code and has a stack that takes up some space in memory. The relation between kernel and userspace threads is 1:1:n, meaning that there can be several pseudo threads running within one userspace thread that maps to one kernel thread. Threads are grouped into tasks by functionality they provide (i.e. several threads implement functionality of one task). Tasks serve as containers of threads, they provide linkage to address space and are communication endpoints for IPC. Finally, tasks can be holders of capabilities that entitle them to do certain sensitive operations (e.g access raw hardware and physical memory).

The scheduler deploys several run queues on each processor. A thread ready for execution is put into one of the run queues, depending on its priority and its current processor, from where it is eventually picked up by the scheduler. Special purpose kernel threads strive to keep processors balanced by thread migration. Threads are scheduled by the round robing scheduling policy with respect to multiple priority run queues.

## 2.2 Memory Management

Memory management is another large subsystem in HelenOS. It serves the kernel to satisfy its own memory allocation requests, provides translation between virtual and physical memory addresses and manages virtual address spaces of userspace tasks.

Kernel allocates memory from the slab allocator, which itself allocates memory from a buddy system based allocator of physical memory frames.

The virtual address translation layer currently supports two mechanisms for mapping virtual memory pages to physical memory frames (i.e. 4-level hierarchical page tables and global page hash table), and is further extensible to other mechanisms. Userspace tasks depend on support of address spaces provided by the kernel. Each address space is a set of mutually disjunctive address space areas. An address space area is usually connected to, and backed by, anonymous memory, executable image of some program or continuous region of physical memory. However, swapping pages in and out to external memory is not supported. Address space areas can be easily shared among address spaces.

## 2.3 IPC

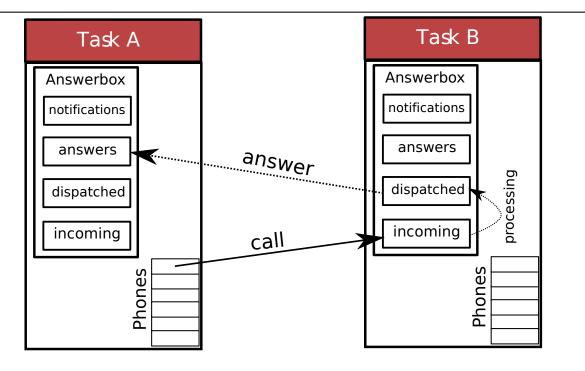

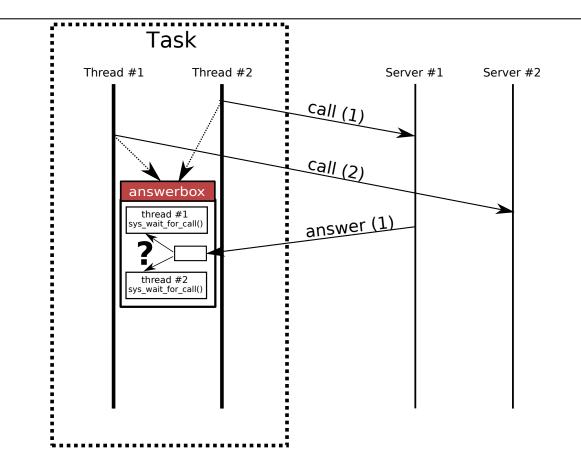

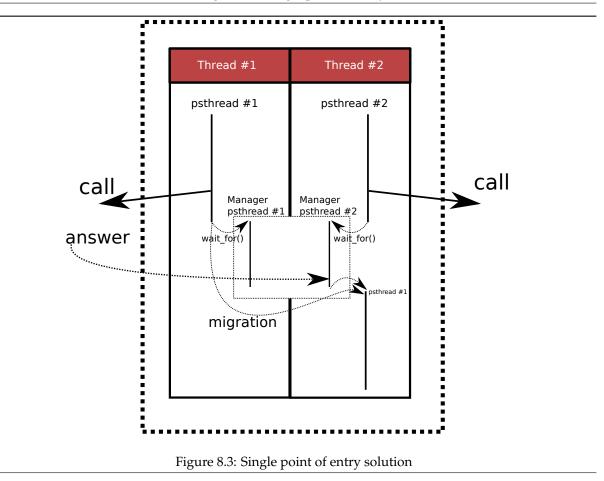

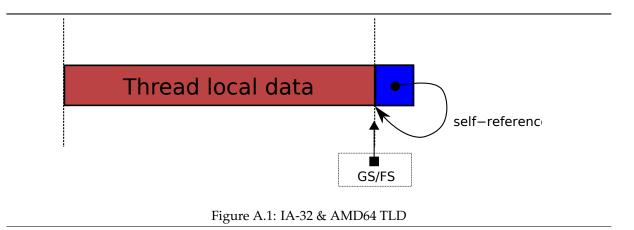

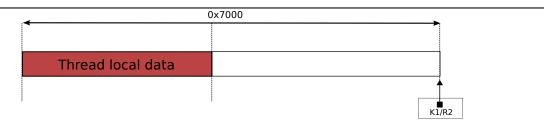

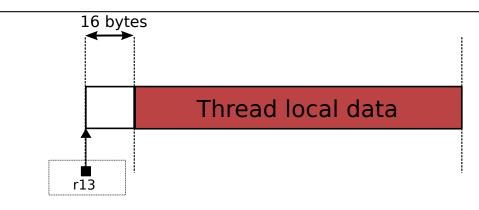

Due to the fact that HelenOS is a microkernel, strong emphasis is put on its IPC (Inter-Process Communication<sup>1</sup>). Tasks communicate by passing very short messages to one another or by sending (i.e. sharing) address space areas when larger data is to be transfered. The abstraction uses terms like phones, calls and answerboxes, but is similar to well-known abstraction of message queues. A task can have multiple simultaneous simplex connections to several other tasks. A connection leads from one of the source task's phones to the destination task's answerbox. The phones are used as handles for making calls to other tasks. Calls are asynchronous and can be forwarded from one task to another.